# A Floating Gate MOSFET Based Novel Programmable Current Reference

V. Suresh Babu, Haseena P. S., Varun P. Gopi, M. R. Baiju

Abstract- In this paper a scheme is proposed for generating a programmable current reference which can be implemented in the CMOS technology. The current can be varied over a wide range by changing an external voltage applied to one of the control gates of FGMOS (Floating Gate MOSFET). For a range of supply voltages and temperature, CMOS current reference is found to be dependent, this dependence is compensated by subtracting two current outputs with the same dependencies on the supply voltage and temperature. The system performance is found to improve with the use of FGMOS. Mathematical analysis of the proposed circuit is done to establish supply voltage and temperature independence. Simulation and performance evaluation of the proposed current reference circuit is done using TANNER EDA Tools. The current reference shows the supply and temperature dependencies of 520 ppm/V and 312 ppm/°C, respectively. The proposed current reference can operate down to 0.9 V supply.

*Keywords*-Floating Gate MOSFET, current reference, self bias scheme, temperature independency, supply voltage independency.

## I. Introduction

PRESENT day high performance analog, digital and power electronic systems require stable, temperature independent current references. For this, many high precision, temperature compensated reference circuits have been proposed and, in particular, many efforts have been made towards developing a reliable voltage and current references in CMOS technology. For supply voltage and current independent biasing, techniques based on band gap reference is most widely used [1]-[3]. In [4], a low temperature coefficient current reference with temperature compensated resistor has been proposed. The different thermal behaviour of the threshold voltage and mobility of MOS transistors in the strong inversion region is utilized in [5] to compensate the temperature dependency. But this reference current is sensitive to supply voltage variations. In [6] two current outputs with

V. Suresh Babu is with the Department of Electronics and Communication Engineering, College of Engineering Idukki, Kerala, India, e-mail: vsbsreeragam@gmail.com

Haseena P. S. is with the Kerala State Electricity Board, Kalamassery, Kerala, India, e-mail: haseena.ps@gmail.com.

Varun P. gopi is with the Department of Electronics and Communication Engineering, Government Engineering College Wayanad, Kerala, India e-mail: varunpg@gecwyd.ac.in

M. R. Baiju is with the Department of Electronics and Communication Engineering, College of Engineering Trivandrum, Kerala, India, e-mail: mrbaiju@ieee.org.

the same supply voltage and temperature dependency are subtracted to obtain a supply and temperature compensated reference current, which shows a large temperature coefficient.

FGMOS based circuit is suitable for low voltage applications as its threshold voltage can be reduced significantly by applying voltage at one of the control gates [7], [8]. The use of floating gate transistor allows programmability of the circuit [7]-[11]. The FGMOS also provides a wide operating range and low voltage operation [10]. In this paper, we propose a FGMOS based self bias current reference circuit. The output currents from two self biased circuits having the same supply voltage and temperature dependency are subtracted to achieve the supply voltage and temperature independence. The proposed circuit shows a temperature coefficient of 312 ppm/0C and supply voltage dependency of 520 ppm/V and it can work with a supply voltage as low as 0.9 V. A mathematical analysis of the proposed circuit is also presented which establishes supply voltage and temperature independence of the circuit.

The content of this paper is organized as follows. In section II, the FGMOS structure is explained. Section III describes the self biasing scheme. Section IV covers the description of the proposed current reference circuit. Section V presents the mathematical analysis of the proposed circuit. The simulation results are presented in section VI and the conclusion is made in section VII.

## II. PRINCIPLE FLOATING GATE MOSFET

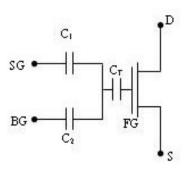

FGMOS Transistor consists of a conventional MOS transistor with its gate surrounded by  $SiO_2$  and capacitively coupled to multiple controlling input gates [12]-[15]. A two input Floating Gate MOSFET is shown in Fig. 1. A dc voltage  $(V_b)$  is applied at the Bias Gate (BG) while the signal is applied at the Signal Gate (SG). Since the gate surrounded by  $SiO_2$  has no dc path to a fixed potential, it is known as Floating Gate, i.e. the floating gate is formed by the first polysilicon layer, while the multiple input gates are formed by the second polysilicon layer located above the floating gate. The conduction of the FGMOS transistor is different from that of conventional MOS transistor with the same terminal potential, due to the capacitive coupling between the Floating Gate (FG) and control gates. When a voltage is applied to the control gate, capacitive coupling between the control gate and FG induces an electrical field on the FG. The induced field on the FG modifies the conductance of the underlying channel region and the effective threshold voltage of the device.

The resultant threshold voltage  $V_T(fg)$  of the FGMOS with respect to signal gate, depends on the threshold voltage of the

Fig 1. Two input Floating Gate MOSFET structure

Floating Gate  $(V_T)$  and is given by [9][10]

$$V_T(fg) = \frac{V_T - V_b k_1}{k_2} \tag{1}$$

where  $k1 = \frac{C_1}{C_T}$ ,  $k2 = \frac{C_2}{C_T}$ ,  $C_1$  and  $C_2$  represent the capacitances between floating gate and control gate respectively,  $C_T$  is the sum of all the capacitances between control gate and floating gate, floating gate to drain, floating gate to source and floating gate to bulk.

#### III. SELF BIAS SCHEME FOR CURRENT REFERENCE

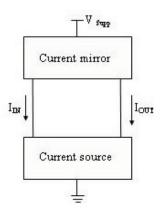

Power supply sensitivity can be greatly reduced by the use of self biasing. The block diagram in Fig. 2 illustrates the concept of self bias [16]. In this scheme, instead of developing the input current by connecting a resistor to the supply, the input current is made dependent directly on the output current of the current source itself. Assuming the feedback loop formed by this connection has a stable operating point, all the current flowing in the circuit is much less sensitive to power-supply voltage than that of the resistively biased case.

Fig 2. Self bias scheme for current reference

# IV. THE PROPOSED CURRENT REFERENCE CIRCUIT

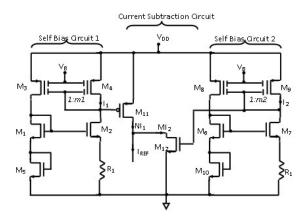

The proposed current reference circuit based on FGMOS is depicted in Fig.3. The circuit consists of two self biased current reference circuits and one current subtraction circuit. The first self bias circuit is made up of the current mirror  $M_3$ –

Fig 3. The proposed current reference circuit

$M_4$  and the current source  $M_1 - M_2 - M_5 - R_1$ . The temperature drift due to  $R_1$  is compensated by placing  $M_5$ , with a voltage drop equal to sum of two terms having opposite temperature coefficients. The current mirror fixes the ratio  $m_1$  (current ratio between  $M_3$  and  $M_4$ ) between the current flowing in the two branches and the current source defines the value of current  $I_1$ . Similarly the second self bias current reference consists of the current mirror  $M_8 - M_9$  which fixes the ratio  $m_2$  (current ratio between  $M_8$  and  $M_9$ ) and the current source  $M_6-M_7-M_{10}-R_1$ which defines the current  $I_2$ . The temperature drift due to  $R_1$  in this circuit is compensated by  $M_{10}$ . The two self biased current references generate  $I_1$  and  $I_2$  respectively. The current mirror  $M_4$  and  $M_{11}$  multiplies  $I_1$ , to get  $NI_1$  and the current mirror  $M_9$  and  $M_{12}$  multiplies  $I_2$  to get  $MI_2$ . Then, by subtracting  $MI_2$  from  $NI_1$ , the supply and temperature compensated output current is obtained.

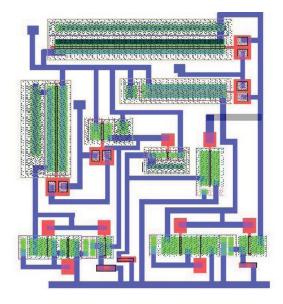

Fig 4. Layout of the proposed current reference circuit

#### V. MATHEMATICAL ANALYSIS

MOS transistors in the proposed circuit works in saturation region. Therefore the drain current I can be expressed in terms of their gate to source voltage as

$$I = \frac{\mu C_{ox}}{2} \frac{W}{L} (V_{GS} - V_T)^2$$

(2)

where  $\mu$  is the mobility of electrons (holes) in NMOS (PMOS) devices,  $C_{ox}$  is the gate capacitance per unit area, W/L is the aspect ratio of the MOS device with W as the gate width and L as the gate length, and  $V_T$  is the threshold voltage. From (2)  $V_{GS}$  is obtained as

$$V_{GS} = V_T + \sqrt{\frac{I}{\beta_0 \alpha}} \tag{3}$$

where  $\beta_0 = \frac{\mu C_{ox}}{2}$  and  $\alpha = \frac{W}{L}$  Applying Kirchoff's voltage law to the current source in the first self biased circuit leads to

$$V_{GS1} + V_{GS5} - V_{GS2} - m_1 R_1 I_1 = 0 (4)$$

Substituting the value of  $V_{GS}$  in (4) results in (5)

$$\sqrt{\frac{I_1}{\beta_0}} \left( \frac{1}{\sqrt{\alpha_1}} + \frac{1}{\sqrt{\alpha_5}} - \sqrt{\frac{m_1}{\alpha_2}} \right) + V_T - m_1 R_1 I_1 = 0$$

(5)

Here the voltage drop across resistor  $R_1$  is given by the sum of two terms with different temperature coefficients. One term is related to the overdrive voltage of the transistors  $M_1$ ,  $M_2$  and  $M_5$  and has a positive temperature coefficient due to the negative temperature drift of mobility, while the other term is the threshold voltage  $V_T$  which has a negative temperature coefficient. Therefore, by properly choosing  $R_1$  a temperature compensated current  $I_1$  is obtained.

Squaring (5),

$$m_1^2 R_1^2 I_1^2 - 2m_1 R_1 I_1 V_T + V_T^2 = \frac{I_1}{\beta_0} \left( \frac{1}{\sqrt{\alpha_1}} + \frac{1}{\sqrt{\alpha_5}} - \sqrt{\frac{m_1}{\alpha_2}} \right)^2$$

(6)

Equation (6) is a quadratic equation in  $I_1$ . Neglecting higher powers of  $R_1$  result in an approximated solution, given by

$$I_1 = \frac{V_T}{m_1 R_1} + \frac{1}{2\beta_0 m_1^2 R_1^2} \left( \frac{1}{\sqrt{\alpha_1}} + \frac{1}{\sqrt{\alpha_5}} - \sqrt{\frac{m_1}{\alpha_2}} \right)^2 \tag{7}$$

Setting  $\alpha_1 = \alpha_2 = \alpha_5 = \alpha$  in (7),

$$I_1 = \frac{V_T}{m_1 R_1} + \frac{1}{\beta R_2^2} \left( \frac{1}{m_1} - \frac{1}{2\sqrt{m_1}} \right)^2 \tag{8}$$

where  $\beta = \beta_0 \alpha$ .

Similarly for the second self bias current reference circuit the current  $I_2$  is given by

$$I_2 = \frac{V_T}{m_2 R_1} + \frac{1}{2\beta_0 m_2^2 R_1^2} \left( \frac{1}{\sqrt{\alpha_6}} + \frac{1}{\sqrt{\alpha_{10}}} - \sqrt{\frac{m_2}{\alpha_7}} \right)^2$$

(9)

In (9), setting  $\alpha_6 = \alpha_7 = \alpha_{10} = \alpha$ ,

$$I_2 = \frac{V_T}{m_2 R_1} + \frac{1}{\beta R_1^2} \left( \frac{1}{m_2} - \frac{1}{2\sqrt{m_2}} \right)^2 \tag{10}$$

The reference current is obtained by subtracting the current  $MI_2$  from  $NI_1$  as in (11)

$$I_{ref} = NI_1 - MI_2 \tag{11}$$

Substitution of (8) and (10) in (11) results in (12)

$$I_{ref} = \frac{V_T}{R_1} \left( \frac{1}{m_1} - \frac{1}{m_2} \right) + \frac{1}{\beta R_1^2} \left[ N \left( \frac{1}{m_1} - \frac{1}{2\sqrt{m_1}} \right)^2 - M \left( \frac{1}{m_2} - \frac{1}{2\sqrt{m_2}} \right)^2 \right]$$

(12)

In (12) as expected, the reference current is independent of supply voltage. Also, due to the negative coefficient of first term and positive temperature coefficient of the second term, temperature dependency is reduced.

#### VI. SIMULATION RESULTS AND DISCUSSION

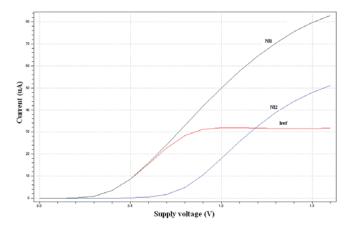

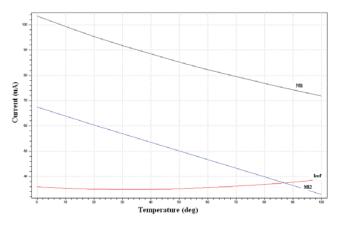

The layout of the proposed circuit is shown in Fig. 4. The layout is prepared by using LEDIT tool provided by TANNER EDA. The simulation of the proposed current reference circuit is carried out using TSPICE in TANNER EDA with BSIM 4.4 model card. Fig. 5 shows the variation of reference current,  $I_{ref}$ ,  $NI_1$  and  $MI_2$  with supply voltage. From this figure we can see that  $I_{ref}$  which is the difference between  $NI_1$  and  $MI_2$ is constant over a range of supply voltages. Fig. 6 shows the variation of  $I_{ref}$ ,  $NI_1$  and  $MI_2$  with temperature. Here also,  $I_{ref}$ is found to be constant over a range of temperature. From these results, temperature coefficient and supply voltage dependence are calculated as 312 ppm/°C and 520 ppm/V respectively. The performance of the proposed current reference circuit is compared with the current reference circuits in [5] and [6] for output current, supply voltage requirement, temperature dependency. The comparison is tabulated in Table I.

Fig 5. Variation of Reference current  $I_{ref}$ ,  $NI_1$  and  $MI_2$  with Supply Voltage

The data in Table I shows that, the proposed circuit has better performance compared to the previous works in terms of supply voltage requirement, supply voltage and temperature dependence of current output.

Fig 6. Variation of Reference current  $I_{ref}$ ,  $NI_1$  and  $MI_2$  with Temperature

TABLE I PERFORMANCE COMPARISON OF CURRENT REFERENCE

| Parameter              | Unit           | Proposed | [5]     | [6]   |

|------------------------|----------------|----------|---------|-------|

| Output current         | $\mu A$        | 31.8     | 13.65   | 10.45 |

| Minimum supply voltage | V              | 0.9      | 2.5     | 1.1   |

| Supply dependency      | ppm/V          | 520      | 4000    | 1700  |

| Temperature dependency | ppm/°C         | 312      | 130     | 720   |

| Temperature Range      | <sup>0</sup> C | 0-100    | -30-100 | 0-120 |

## VII. Conclusion

A novel FGMOS based current reference is proposed in this paper. The dependence of current reference on supply voltage and temperature is compensated by subtracting two current outputs having same dependencies on supply voltage and temperature. Mathematical analysis also establishes the same. The layout of the proposed current reference circuit is prepared using LEDIT tool provided by TANNER EDA. TSPICE simulation results using BSIM 4.4 model card are presented. Simulation result shows that the reference current has a temperature dependency of 312 ppm/°C in the temperature range 0-100°C and a supply dependency of 520 ppm/V. The circuit is found to be operating at a supply voltage as low as 0.9 V.

## REFERENCES

- [1] Ye, R. W., and Tsividis, Y. P., "Bandgap voltage reference sources in CMOS technology", *Electron. Lett.*, vol. 18, pp. 24-25, 1982.

- [2] R. Dehghani, S. M. Atarodi, "A new low voltage precision CMOS current reference with no external components", *IEEE Trans. Circuits Syst. II*, vol. 50, no.12, pp. 928-932, Dec. 2003.

- [3] Bendali, A., and Audet, Y., "A 1-V CMOS current reference with temperature and process compensation", *IEEE Trans. Circuits Syst. I*, vol. 54, no. 2, pp. 1424-1429, 2007.

- [4] J. Chen and B. Shi, "1 V CMOS current reference with 50 ppm/OC temperature coefficient", Electron. Lett., vol. 39, pp. 209-210, Jan. 2003.

- [5] F. Fiori, P. S. Crovetti, "A new compact temperature-compensated CMOS current reference", *IEEE Trans. Circuits Syst. II: Exp. Briefs*, vol. 52, no. 11, pp. 724-728, Nov. 2005.

- [6] C. Yoo, J. Park, "CMOS current reference with supply and temperature compensation", Electronic letters, IET Jour. Vol. 43, Issue 25, Dec. 2007.

- [7] J. Ramirez-Angulo, S. C. Choi, G. Gonzalez-Altamirano, "Low Voltage OTA Architecture Using Multiple Input Floating Gate Transistor", J. IEEE Trans. Circuits Syst., vol. 42, no. 12, pp. 971-974, Nov. 1995.

- [8] E. Sanchez-Sinencio, A. G. Andreou, "Low Votage/Low Power Integrated Circuits and Systems", *IEEE Press.*, 1999.

- [9] S. S. Rajput, S. S. Jamuar, "Design Techniques For Low Voltage Analog Circuits Structures", NSM2001/IEEE, Malaysia, Nov. 2001.

- [10] Susheel Sharma, S. S. Rajput, L. K. Magotra, S. S. Jamuar, "FGMOS based wide range low voltage current mirror and its applications", *Circuits and systems*, APCCAS'02, 2002 Asia-Pacific Conference, Vol. 2, pp. 331- 334, Oct. 2002.

- [11] V. Suresh Babu, Rose Katherine A. A., M. R. Baiju, "Adaptive Neuron Activation Function with FGMOS Based Operational Transconductance Amplifier", Proceedings of IEEE Computer Society, Annual Symposium on VLSI, April 2007.

- [12] P. Hasler, T. S. Lande, "Overview of floating gate devices, circuits and systems", *IEEE J. Solid State Circuits*, vol. 48, no.1, pp. 1-3, Jan 2001.

- [13] Paul Hasler. "Floating Gate Devices, Circuits, and Systems", *IEEE Cmputer society*, Proc. 9th International Database Engineering and Applications Symp., 2005.

- [14] S. Tuan Wang, "On the I-V characteristics of floating gate MOS transistor", *IEEE Trans. Elect. Devices*, vol. 26, no. 9, pp. 1292-1294, Sept. 1979.

- [15] Venkatesh Srinivasan, G. Serrano, C. M. Twigg, Paul Hasler, "A Floating gate Based Programmable CMOS reference", *IEEE Trans. Circuits Syst. I*, Reg. Papers, vol. 55, no. 11, pp. 3448-3456, Dec. 2008.

- [16] P. Gray, P. J. Hurst, S. H. Lewis, R. G. Meyer, "Analysis and Design of Analog Integrated Circuits", 4th ed. Hoboken, NJ: Wiley, 2001.

Dr. V. Suresh Babu received the B. Tech. Degree in Electronics and Communication Engineering from Kerala University, Trivandrum, India, in 1989, the M. Tech. Degree in Integrated Electronic Devices and Circuits from IIT Madras in 1996 and the Ph.D. Degree in Electronics and Communication in 2013 from Kerala University. From 1990 to 1991, he was with the Kerala State Electronics Development Corporation Ltd., Trivandrum, India. Since 1991, he has been a member of the faculty of the Department of Electronics and Communication Engineering, in

Government Engineering Colleges in Kerala. Presently he is Associate Professor in Government Engineering College, Painavu, Idukki, Kerala, India. His areas of interest are Analog Circuit Design and VLSI Signal Processing.

Haseena P. S. received the B. Tech. Degree in Electronics and Communication Engineering from College of Engineering Adoor in 2001 and M. Tech. in Electronics and Communication Engineering (specialization in Microwave and Television) from College of Engineering Trivandrum, India in 2009, respectively. Currently she is working as an Assistant Engineer Kerala State Electricity Board, India. Her areas of research are Microwave, Wireless Communication and VLSI systems.

Dr. VARUN P. GOPI received the B. Tech. Degree in Electronics and Communication Engineering from Amal Jyothi College of Engineering, Kanjirappally, India in 2007 and M. Tech. in Electronics and Communication Engineering (specialization in Signal Processing) from College of Engineering Trivandrum, India in 2009 and Ph.D. Degree in Signal Processing from National Institute of Technology (NIT), Triuchirappalli, Tamilnadu, India in 2014, respectively. Currently he is working as an Assistant Professor in the department of Electronics

and Communication Engineering, Government Engineering College Wayanad, Kerala, India. His areas of research are Signal and Image Processing, Analog Circuit Design, VLSI systems, Wireless communication, Compressed sensing.

**Dr. M. R. Baiju** received the B. Tech. Degree in Electronics and Communication Engineering from College of Engineering, Trivandrum, India, in 1988, and the M. Tech. Degree in Electronics Design and Technology and the Ph.D. Degree in Power Electronics from the Center for Electronics Design and Technology, Indian Institute of Science, Bangalore, India, in1997 and 2004, respectively. From 1988 to 1991, he was with the National Thermal Power Corporation Ltd., New Delhi, India. Since 1991, he has been a member of the faculty of

the Department of Electronics and Communication Engineering, College of Engineering, Trivandrum, Kerala. His areas of interest are Multilevel Inverter Control strategies, MEMS and VLSI systems.