# A Novel Approach of Multilevel Inverter with Reduced Power Electronics Devices

M. Jagabar Sathik, K. Ramani

Abstract—In this paper family of multilevel inverter topology with reduced number of power switches is presented. The proposed inverter can generate both even and odd level. The proposed topology is suitable for symmetric structure. The proposed symmetric inverter results in reduction of power switches, power diode and gate driver circuits and also it may further minimize the installation area and cost. To prove the superiority of proposed topology is compared with conventional topologies. The performance of this symmetric multilevel inverter has been tested by computer based simulation and prototype based experimental setup for nine-level inverter is developed and results are verified.

**Keywords**—Cascaded H- Bridge (CHB), Multilevel Inverter (MLI), Nearest Level Modulation (NLM), Total Harmonic Distortion (THD).

#### I. INTRODUCTION

In recent era, the multilevel inverter is state of art power conversion system for high voltage and high power quality applications. The two-level inverter with semiconductor technology may not suit for high voltage application which may increase the high voltage stress on switch, high Electro Magnetic Interference (EMI) and poor power quality output [1], [2]. In order to solve these issues the conventional multilevel inverters are introduced, but it may require high number of power semiconductor devices. So, the researchers are developing new multilevel inverter topologies with existing semiconductor technology to meet require high power quality with reduced power semiconductor devices [3]. Because of these advantages multilevel converters are more attractive in high power applications. However, the important benchmark for designing multilevel inverters is listed below.

- Low voltage stress on switches

- Low Electromagnetic interference.

- Low Harmonic Distortion

- Absence of LC Filter

- Modularity

- More redundant state

- Reliability

- Low Cost

The conventional multilevel inverter topologies are (i) Neutral Point Clamped (NPC) (ii) Flying Capacitor (FC) and (iii) Cascaded H-Bridge (CHB). These converters provide

Jagabar Sathik Mohd.Ali is Assistant Professor at J.J College of Engineering and Technology Tiruchirappalli, India (phone: +91-9500525422; e-mail: jagabarsathik@ gmail.com).

Dr.K.Ramani is Associate Professor at K.S.Rangasamy College of Technology Tiruchengode, India (phone: +91-9788518536; e-mail: kreee82@gmail.com).

better output quality by increasing smaller voltage level; they are applied for commercial applications and industrial applications like AC Drives and FACTS Devices [4]. Theoretically, these topologies are capable of generating infinite number of equal stepped voltage level. Whereas, practically, the number of level increases as it requires more number of power switches, clamping diode, flying capacitor and associated components respectively. Furthermore, this may increase the installation area, cost of the converter and complex control circuits. In last few decades several authors were finding solution by introducing novel multilevel inverter topologies with reduction of power switches [5]-[8]. In symmetrical method all the dc sources voltage have unique value and it ensures good modularity. Different rating of switches are required in asymmetrical method due to different dc sources voltage magnitude, this may generate high number of output voltage with minimum dc source. But multilevel inverter modularity may reduce. An Attempt has been made in [9] to propose a new multilevel inverter topology with reduced power switches. This converter required different voltage rating of power switches. In addition, the voltage stress on the switches will be high for higher number of levels. Novel multilevel inverter topology is proposed in [10]. This topology is combination of both power diodes and IGBT. In this method, the more number of power switches is reduced but it may require more numbers of power diodes, which may produce voltage spikes at load. In such a way several multilevel inverter are proposed with own advantage and disadvantages [11]-[14]. Aforementioned literatures are considered for symmetric topology only.

## II. PROPOSED TOPOLOGY

In this section, detailed explanation of two different basic structures of proposed topologies are introduced and mathematical expression for number of voltages level  $(N_{Step})$ , Number switches  $(N_{Switch})$  and number of dc sources voltages calculation are presented.

### A. Suggested Topology

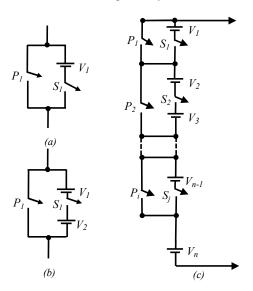

The basic double and single source unit is shown in Figs. 1 (a) & (b).  $V_{dcn}$  &  $V_{dc(n-1)}$  is connected in series with  $S_I$  switch and Parallel with  $P_I$ . Fig. 1 (c) shows the generalized basic structure of proposed topology which is the combination of both the single and double source basic unit.  $N_S$  is the number of dc source voltages, which are separated with series connected unidirectional controlled power switches are termed as voltage adder  $(S_I, S_2, S_3....S_n)$  and also each dc sources are connected with parallel switches are termed as subtractor  $(P_I, S_I)$

P2, P3....  $P_n$ ). The  $n^{th}$   $V_{dc}$  is represented as  $V_{dcn}$ . In proposed method  $V_{dcn}$  is not connected with any parallel switches,  $V_{dcn-1}$  and  $V_{dcn-2}$  are connected together with parallel switch of  $P_n$ , remaining each dc sources voltages are connected with series/parallel combination respectively.

Fig. 1 Proposed Symmetric Topology (a) Basic single source basic unit (b) Basic double source basic unit (c) Generalized structure for odd and even number of sources

The corresponding switches will be fired to synthesize positive stepped waveform. The series/parallel unit is connected series with H-bridge, which is used to create a current flow in both directions at load terminals. Fig. 1 shows the generalized structure of new symmetrical topology is proposed for  $N_{Step}$  with equal dc sources Values  $(V_{dc})$ . The topology constructed with unidirectional (arrangement of series/parallel connection) power switch along with series connection of equal dc sources which are connected with the H-bridge. The proposed topology is separated into two units (i) combined adder/subtractor switches with dc voltage source is termed level generator unit (ii) Polarity changer H-Bridge unit. The switch  $(P_n)$  is connected parallel with two dc sources ( $V_{dcn-1}$ ,  $V_{dcn-2}$ ) as shown in Fig. 2. According to Fig. 1 the IGBTs of  $(S_1, P_1)$ ,  $(S_2, P_2)$  · ·  $\cdots$   $(S_{n-1}, P_n)$  turn on simultaneously the  $V_{dc1}, V_{dc2}, \dots V_{dcn-1}$  will be short circuited with same dc source. Either one of the corresponding adder/subtractor switches will turn ON and turn OFF from the Table I.

The maximum output voltage  $(V_{o,max})$  is sum of all the DC source voltage is given:

$$V_{o,max} = V_{dc1} + V_{dc2} + V_{dc3} + \dots + V_{dcn}$$

(1)

$$V_{o,max} = \sum_{i=1}^{n} V_{dcn} \tag{2}$$

Equations (1) & (2) illustrate the output level of adder/ Subtractor circuit. Both the positive and negative levels synthesized by the H-bridge circuit, at load  $(V_{o, Load})$  synthesized stepped output voltage level will be obtained as mentioned below

$$V_{o,max} = \begin{cases} \sum_{i=1}^{n} + V_{dcn} & , H_{S1}, H_{S4} = 1\\ \sum_{i=1}^{n} -V_{dcn} & , H_{S2}, H_{S3} = 1 \end{cases}$$

(3)

In this proposed topology, the number of output voltage levels  $(N_{Step})$ , number of IGBT  $(N_{Switch})$  and the number of DC sources  $(N_s)$  are calculated as follows, respectively:

$$N_{Step} = 2N_S + 1 \tag{4}$$

Still, the proposed topology structure varies with the odd and even number of DC sources and therefore it is necessary to express the requirement of number of IGBT for given output levels and for given number of DC sources is given below:

$$N_{Switch} = \begin{cases} N_S + 5 & , N_S = odd \\ N_S + 4 & , N_S = even \end{cases}$$

(5)

#### B. Power Stage Operation:

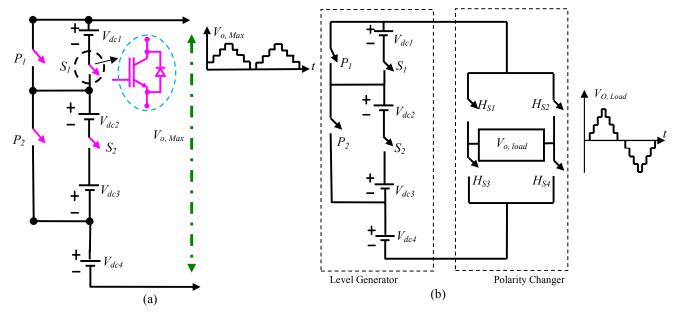

In this section, 9-level symmetric multilevel inverter is explained to understand the proposed topology. In order to provide more number of output voltage steps with minimum number of switches by using proposed symmetric topology as shown in Fig. 2 The magnitude of the each steps are calculated for 9-level inverter is shown in below.

$$V_{dc1} = P_1 + P_2 V_{dc2} = P_2 + S_1 V_{dc3} = P_1 + S_2 V_{dc4} = S_2 + S_1$$

(6)

where  $P_1 = V_{dc}$  &  $P_2=2V_{dc}$  (i.e.)  $P_1$  will subtract the  $V_{dc}$  voltage and  $P_2$  will subtract  $2V_{dc}$  voltage respectively. To obtain a nine level output voltage, the mathematical equations are expressed in (6). Each dc voltage sources are subtracted with corresponding ON state parallel switches (Subtractor switch). The theoretical explanations as follows: The H-bridge inverter is series connected with polarity generator which can produce possible five positive output levels from 0 to maximum peak value of  $4V_{dc}$ , In H-bridge inverter switches will create the current path to load in both positive and negative direction by switching corresponding switches ( $H_{SI}$ &  $H_{S4}$ ) &  $(H_{S2}$ &  $H_{S3}$ ). From Table I, the corresponding switches will be on and off to produce the stepped waveform. The H-Bridge should withstand for sum of all the dc sources, which may increase the voltage rating of switches and cost of the inverter. Here worth to mention that the number of IGBTs are reduced, which reduce the cost of the switches, gate driver circuits and other supporting components.

Fig. 2 Proposed 9-Level inverter (Even Sources) (a) Level generator circuit (b) with polarity changer

TABLE I SWITCH STATES OF 9-LEVEL PROPOSED TOPOLOGY

| Switch States    |                |       |       |          |          |          |          | Voltage level at V                      |  |

|------------------|----------------|-------|-------|----------|----------|----------|----------|-----------------------------------------|--|

| $\mathbf{P}_{1}$ | P <sub>2</sub> | $S_1$ | $S_2$ | $H_{S1}$ | $H_{S2}$ | $H_{S3}$ | $H_{S4}$ | Voltage level at V <sub>o,Load</sub>    |  |

| 1                | 1              | 0     | 0     | 1        | 0        | 0        | 1        | $+V_{dc4}$                              |  |

| 0                | 1              | 1     | 0     | 1        | 0        | 0        | 1        | $+V_{dc4}+V_{dc1}$                      |  |

| 1                | 0              | 0     | 1     | 1        | 0        | 0        | 1        | $+V_{dc2}+V_{dc3}+V_{dc4}$              |  |

| 0                | 0              | 1     | 1     | 1        | 0        | 0        | 1        | $+V_{dc1}+V_{dc2}+V_{dc3}+V_{dc4}$      |  |

| 0                | 0              | 0     | 0     | 1        | 1        | 0        | 0        | 0                                       |  |

| 1                | 1              | 0     | 0     | 0        | 1        | 1        | 0        | $-V_{dc4}$                              |  |

| 0                | 1              | 1     | 0     | 0        | 1        | 1        | 0        | $-\left(V_{dc4}\!\!+\!\!V_{dc1}\right)$ |  |

| 1                | 0              | 0     | 1     | 0        | 1        | 1        | 0        | $-(V_{dc2}+V_{dc3}+V_{dc4})$            |  |

| 0                | 0              | 1     | 1     | 0        | 1        | 1        | 0        | $-(V_{dc1}+V_{dc2}+V_{dc3}+V_{dc4})$    |  |

## III. NEAREST LEVEL MODULATION TECHNIQUE

There are several modulation techniques proposed for multilevel inverter.

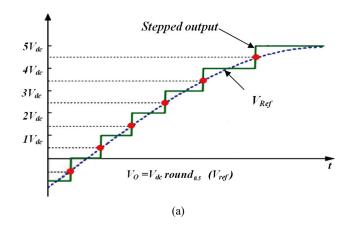

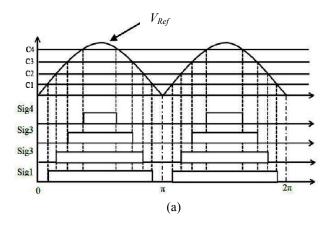

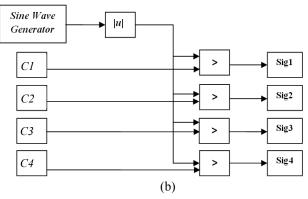

Fig. 3 Nearest level selection: (a) Level synthesis and (b) control diagram

Some of the well known modulation techniques are Fundamental Switching Method [15], Carrier Based Pulse Width Modulation (CBPWM) Techniques [16], Space Vector Pulse Width Modulation (SVPWM) [17], Selective Harmonic Elimination Method [18], Hysteresis Modulation [19] and Hybrid Modulation Techniques [20]. These modulation techniques are successfully implemented in industrial for different applications like AC Drives [21], [22], FACTS and Renewable Energy.In this paper, the Conventional NLM is used, which is generate steps with base concept of round off technique as shown in Fig. 3. This is suitable for higher number of output voltage level. This is easily performed using the round {} function and integer closest to x. Since this is like half height method, the additional convention is that halfintegers are always rounded to even number. The largest possible error is then limited by  $V_{dc}/2$ .

The main switching angles are determined by the following equation:

$$\alpha_i = Sin^{-1} \left( 2i - \frac{1}{m-1} \right)$$

Where  $i = 1, 2, \dots \frac{m-1}{2}$  (7)

where  $\alpha_i$  is switching angle and m is Number of output voltage level.

## IV. COMPARISON WITH OTHER TOPOLOGIES

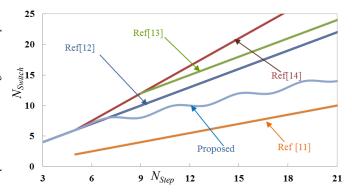

This paper main objective is to reduce the number of power switches in multilevel inverter. As shown Fig. 4, the comparison between  $N_{Step}$  Vs  $N_{Switches}$  is presented. The proposed topology required less number of switches than other topologies. In [11] is required minimum number of IGBT compared to proposed inverter. But it may require high number of power diode. Addition to this, the voltage spike will occur at load side due to interloping in diode (Reverse recovery problem). To avoid this issue (i) the load R value should be higher than L value and (ii) should use LC filter at output side. So, this may not suitable for highly inductive load.

Fig. 4 Comparison of Number of Steps against Number of Switches

The proposed novel symmetric multilevel inverter has significant improvements compared to conventional Cascaded Multilevel Inverter. In Table II, the parameters such as Peak Inverse Voltage (*PIV*), Number of switches and DC sources are listed.

TABLE II

COMPARISON OF POWER COMPONENT REQUIREMENT FOR CONVENTIONAL

CASCADED AND PROPOSED MULTILEVEL INVERTER

| Parameters                  | Conventional<br>Cascaded Inverter | Proposed                      |

|-----------------------------|-----------------------------------|-------------------------------|

| No.of DC Sources            | Ns                                | Ns                            |

| No.of Switches              | 4Ns                               | Ns+4 for even<br>Ns+5 for odd |

| No.of Output Voltage Levels | 2Ns+1                             | 2Ns+1                         |

| PIV <sup>pu</sup>           | 4Ns                               | 6Ns-2                         |

#### V. SIMULATION AND EXPERIMENTAL RESULTS

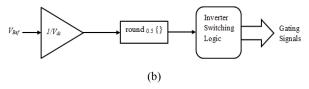

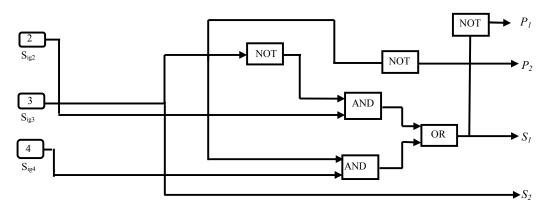

To validate the good performance of the proposed 9-level inverter, the simulation studies are carried out for symmetrical multilevel inverter. The simulation has done by MATLAB/Simulink software. The switching pattern is developed based on the on state switches with K-map as shown in Fig. 5. To generate stepped waveform the conventional Nearest Level method is used. In this method the constant values (C1,C2...Cn) are compared with absolute sine waveform  $(V_{ref})$  to generate appropriate signals as shown in Figs. 6 (a) & (b).

$$C1 = 0.5$$

$C2 = 1 + 0.5$

$C3 = 2 + 0.5$

for  $n^{th}$  Level

$Cn = n - 1 + 0.5$  where  $n = {N_{Level}} - {1 \over 2}$

Fig. 5 Switching Pattern for Proposed Topology from generated Signals

Fig. 6 (a) Nearest Voltage Level Control Technique as a sum of 9-Levels; (b) Switching Signals generation Logic

The simplified switching states are expressed as follows.

$$S_1 = Sig_2 \overline{Sig}_3 + Sig_3 Sig_4 \tag{9}$$

$$S_2 = Sig_3 \tag{10}$$

$$P_I = \overline{S}_I \tag{11}$$

$$P_2 = \overline{S}_2 \tag{12}$$

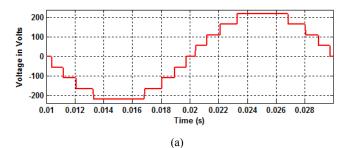

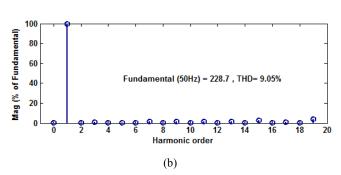

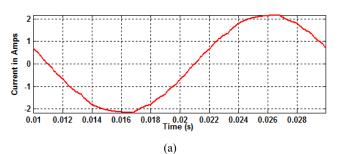

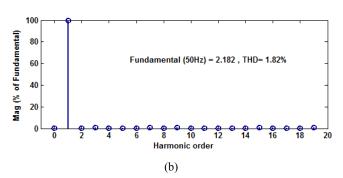

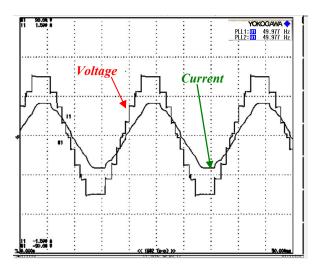

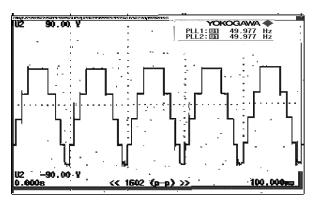

where  $Sig_1$ ,  $Sig_2$ ,  $Sig_3$  and  $Sig_4$  are represent the signals obtained after comparison of constant values. These signals are chosen as a variable for K-map and after simplification the corresponding switching signals is obtained refer to (9) - (12). The simulated output voltage and current waveforms along with harmonic spectrum as shown in Figs. 7 and 8 respectively. In simulation the THD values for voltage and current is 9.05% and 1.82 % respectively. The experimental output voltage and current is shown in Fig. 9. In simulation each dc source has values of 55V (i.e. sum of 220V) and in hardware arrangement has the value of dc input voltage is 15V (i.e. sum of 60V). But both simulation and experimental has same values of R=100 and L=100mH. The experimental maximum output voltage  $V_{O, Max}$  is 60V as shown in Fig. 10.

Fig. 7 (a) Simulation output voltage waveform (b) Voltage harmonic spectrum

Fig. 8 (a) Simulation output current waveform (b) Current harmonic spectrum

Fig. 9 Experimental output voltage & current waveform

Fig. 10 Experimental level generator output voltage

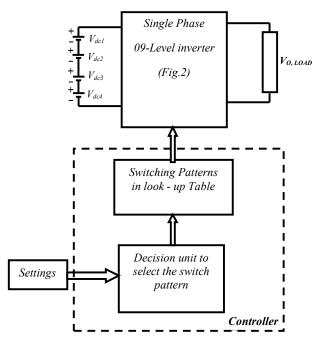

In [23] presented the novel multilevel inverter topology (named as Reduced Switch Cascaded Multilevel Inverterwith reduced switch count. In this, simulation based Total Harmonic Distortion (THD) is compared with Conventional Cascaded Multilevel Inverter (CCMLI). For multilevel inverter applications, carrier based PWM techniques with multiple carriers such as (i) Phase Disposition (PD), (ii) Inverted Phase Disposition (IPD), (iii) Phase Opposition Disposition (POD) and (iv) Alternative Phase Opposition Disposition (APOD) are used to generate appropriate PWM signals. These modulation techniques are implemented for different carriers such as the triangular multicarrier wave, saw tooth multicarrier wave and unipolar sine multicarrier wave. In Table III listed the comparison % THD for proposed topology with presented in [23]. In this paper fundamental switching frequency (NLM) method is used. The comparison of fundamental switching technique with other techniques is shown in Table III. In this table all the other PWM strategies are produced high % THD compared to fundamental switching technique. The control block diagram of overall system is shown in Fig. 11.

TABLE III

COMPARISON OF % THD FOR PROPOSED AND OTHER TOPOLOGIES

| Topology                                  |      | CCMLI | RSCMLI | Proposed<br>MLI |

|-------------------------------------------|------|-------|--------|-----------------|

|                                           | PD   | 13.75 | 13.43  | _               |

| Triangular<br>(Switching Frequency        | IPD  | 13.80 | 14.07  |                 |

| (Switching Frequency 2KHz)                | POD  | 13.92 | 13.83  |                 |

| 21(112)                                   | APOD | 14.04 | 13.37  |                 |

|                                           | PD   | 13.45 | 13.87  |                 |

| Saw Tooth                                 | IPD  | 13.45 | 14.16  |                 |

| (Switching Frequency 2KHz)                | POD  | 13.37 | 13.91  | -               |

| 21(112)                                   | APOD | 13.22 | 14.09  |                 |

|                                           | PD   | 14.56 | 15.79  |                 |

| Unipolar Sine                             | IPD  | 14.56 | 13.88  |                 |

| (Switching Frequency<br>2KHz)             | POD  | 15.59 | 14.14  |                 |

| ZKHZ)                                     | APOD | 14.55 | 14.55  |                 |

| Fundamental switching<br>Frequency (50Hz) | -    | 13.80 | 13.92  | 9.05            |

Fig. 11 Control block diagram for proposed method

#### VI. CONCLUSION

In this paper, the novel symmetric multilevel inverter is proposed. This multilevel inverter can be implemented in industrial where the minimum switches are required. The voltage output and current is verified to confirm the performance of proposed multilevel inverter. The nearest level modulation technique is implemented. Future work on this proposed topology considers: (i). High voltage applications by cascading the proposed topology. (ii) In practical applications such as, Induction motor drives and FACTS controllers.

#### ACKNOWLEDGMENT

The authors want to thank AICTE New Delhi for the support given to this work through the research work and awarded the "Career Award for Young Teachers" *Dr.K.Ramani* (F.No.11.8/AICTE/RIFD/CAYT/POL-I/2013-14)

#### REFERENCES

- [1] Rodriguez, J., Jih-Sheng Lai, Fang Zheng Peng, "Multilevel inverters: a survey of topologies, controls, and applications," *IEEE Trans. Ind. Electron*, vol.49, no.4, pp.724-738, Aug.2002.

- [2] Choi, N.S., Cho, J.G., Cho, Gyu H., "A general circuit topology of multilevel inverter," in *Conf. Rec. 1991 IEEE Power Electronics Specialists Conference*, pp.96-103.

- [3] Kouro, S., Malinowski, M., Gopakumar, K., Pou, J., Franquelo, L.G., Bin Wu, Rodriguez, J., Perez, M.A., Leon, J.I., "Recent Advances and Industrial Applications of Multilevel Converters," *IEEE Trans.Ind. Electron*, vol.57, no.8, pp.2553-2580, Aug. 2010.

- [4] Franquelo, L.G., Rodriguez, J., Leon, J.I., Kouro, S., Portillo, R., Prats, M.A.M., "The age of multilevel converters arrives," *IEEE Ind. Electro. Magazine*, vol.2, no.2, pp.28-39, June 2008.

- [5] Zinoviev, G.S., Lopatkin, N.N., "Evolution of multilevel voltage source inverters," in *Conf. Rec 2008 Actual Problems of Electro. Instr. Eng.*, vol.01, no., pp.125-136, 23-25 Sept.2008.

- [6] Ebrahim Babaei, Seyed Hossein Hosseini, "New cascaded multilevel inverter topology with minimum number of switches," *Energy Conversion and Management*, Vol.50, Issue11, Nov. 2009.

- [7] Farhadi Kangarlu, M., Babaei, E., "Cross-switched multilevel inverter: an innovative topology," IET *Power Electro*, vol.6, no.4, pp.642-651, April 2013.

- [8] Kangarlu, M.F., Babaei, E., Sabahi, M., "Cascaded cross-switched multilevel inverter in symmetric and asymmetric conditions," *IET Power Electron.*, vol.6, no.6, pp.1041-1050, July 2013.

- [9] Kangarlu, M.F., Babaei, E., "A Generalized Cascaded Multilevel Inverter Using Series Connection of Submultilevel Inverters," *IEEE Trans. Power Electron.*, vol.28, no.2, pp.625-636, Feb. 2013.

[10] Mokhberdoran, A., Ajami, A., "Symmetric and Asymmetric Design and

- [10] Mokhberdoran, A., Ajami, A., "Symmetric and Asymmetric Design and Implementation of New Cascaded Multilevel Inverter Topology," *IEEE Trans. Power Electron*, vol.29, no.12, pp.6712-6724, Dec. 2014.

- [11] Yuanmao Ye, Cheng, K.W.E., Junfeng Liu, Kai Ding, "A Step-Up Switched-Capacitor Multilevel Inverter with Self-Voltage Balancing," *IEEE Trans.Ind. Electron*, vol.61, no.12, pp.6672-6680, Dec. 2014.

- [12] Babaei, E., Gowgani, S.S., "Hybrid Multilevel Inverter Using Switched Capacitor Units," *IEEE Trans. Ind. Electron*, vol.61, no.9, pp.4614-4621, Sept. 2014.

- [13] Ali Ajami, A. Mokhberdoran, M.R. Oskuee," A New Topology of Multilevel Voltage Source Inverter to Minimize the Number of Circuit Devices and Maximize the Number of Output Voltage Levels," *J Electr Eng Technol*" Vol. 8, No. 6, Nov.2013.

- [14] Ali Ajami, M.R. Oskuee , A. Mokhberdoran, M. T. Khosroshahi "Advanced Cascade Multilevel Converter with Reduction in Number of Components," *J Electr Eng Technol*" Vol. 9, No. 1, Jan.2014.

- [15] Kouro, S., Bernal, R., Miranda, H., Silva, C.A., Rodriguez, J., "High-Performance Torque and Flux Control for Multilevel Inverter Fed Induction Motors," *IEEE Trans. Power Electron.*, vol.22, no.6, pp.2116-2123, Nov. 2007.

- [16] McGrath, B.P., Holmes, D.G., "Multicarrier PWM strategies for multilevel inverters," *IEEE Trans.Ind. Electron.*, vol.49, no.4, pp.858-867, Aug. 2002.

- [17] Aneesh, M.A.S., Gopinath, A., Baiju, M.R., "A Simple Space Vector PWM Generation Scheme for Any General n -Level Inverter," *IEEE Trans.Ind.Electron.*, vol.56, no.5, pp.1649-1656, May.2009.

- [18] Li, L., Czarkowski, D., Liu, Y., Pillay, P., "Multilevel selective harmonic elimination PWM technique in series-connected voltage inverters," in *Conf.Rec* 1998 IEEE Industry Applications Conference, vol.2, pp.1454-1461.

- [19] Shukla, A., Ghosh, A., Joshi, A., "Hysteresis Modulation of Multilevel Inverters," *IEEE Trans. Power Electron.*, vol.26, no.5, pp.1396-1409, May 2011.

- [20] Govindaraju, C., Baskaran, K., "Efficient Sequential Switching Hybrid-Modulation Techniques for Cascaded Multilevel Inverters," *IEEE Trans. Power Electron.*, vol.26, no.6, pp.1639-1648, June 2011.

- [21] Ramani, K., Rathinam, A., Krishnan, K., "An Enhanced Flying Capacitor Multilevel Inverter Fed Induction Motor Drive," ACEEE International Journal on Electrical and Power Eng., vol. 1, no. 2, pp. 22-26, July 2010.

- [22] Ramani, K., Krishnan, K.," High Performance of Sinusoidal Pulse width Modulation Based Flying Capacitor Multilevel Inverter Fed Induction Motor Drive," *International Journal of Computer Applications.*, vol.1, no.24,pp.116-121, Aug.2010.

[23] Nagarajan, R., Saravanan, M., "Performance Analysis of a Novel Reduced Switch Cascaded Multilevel Inverter", *Journal of Power Electronics.*, vol.14,no.1,pp.48-60,Jan. 2014.

Mohd.Ali Jagabar Sathik was born in Tamil Nadu, India, in 1979.He received the Under graduate degree in Electronics & Communication Engineering from Madurai Kamaraj University, Madurai, India, in 2002 and the Master degree in power electronics and drives from Anna University, Chennai, India, in 2004. He is currently working toward the Ph.D. degree in Faculty of Electrical engineering, Anna University, India .In 2011, He joined the Dept. of Electrical and Electronics

Engineering, J.J. College of Engineering and Technology, Tiruchirappalli, India. His major fields of interest include the analysis and control of power electronic converters and renewable energy systems.

**Dr.K.Ramani** was born in Vedaranyam in 1982. He is graduated in 2004 from Bharathiar University, Coimbatore and post graduated in 2006 at Anna University, Chennai and the Ph.D. degree in Electrical Engineering from Anna University in 2012. He is currently working as an Associate Professor in the department of EEE at K.S.Rangasamy College of Technology, Tiruchengode from January 2006 onwards. He published 56 international/national conferences,

journals. His research interest involves in power electronics, inverter, modeling of induction motor and optimization techniques. He is guiding UG, PG Students also supervised Ph.D scholars in Anna University. He is an ISTE, IETE and IEEE member. He is a awardees CAYT from AICTE, New Delhi. He is acting many editorial board and editor in chief in international journals and IEEE Conferences.