# High Efficiency Class-F Power Amplifier Design

Abdalla Mohamed Eblabla

**Abstract**—Due to the high increase in and demand for a wide assortment of applications that require low-cost, high-efficiency, and compact systems, RF power amplifiers are considered the most critical design blocks and power consuming components in wireless communication, TV transmission, radar, and RF heating. Therefore, much research has been carried out in order to improve the performance of power amplifiers. Classes-A, B, C, D, E and F are the main techniques for realizing power amplifiers.

An implementation of high efficiency class-F power amplifier with Gallium Nitride (GaN) High Electron Mobility Transistor (HEMT) was realized in this paper. The simulation and optimization of the class-F power amplifier circuit model was undertaken using Agilent's Advanced Design system (ADS). The circuit was designed using lumped elements.

**Keywords**—Power Amplifier (PA), Gallium Nitride (GaN), Agilent's Advanced Design system (ADS) and lumped elements.

### I. SIMULATION METHODOLOGY CLASS-F PA DESIGN AND CHOOSING OF OPERATION FREQUENCY

TO configure and design class-F PA, a non-linear model, EGN030MK GaN-HEMT by Modelithics was used. This model is prepared for use to operate from 0.1 to 4.0 GHz with low current, wide band and high power design [5]. Hence, 1.7GHz was chosen as an operation frequency in this paper.

#### A. Choice of Bias Point

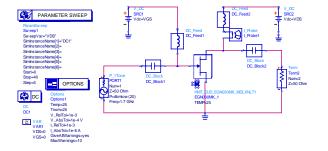

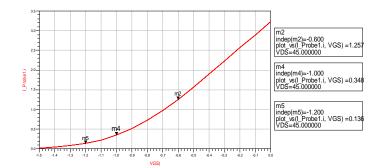

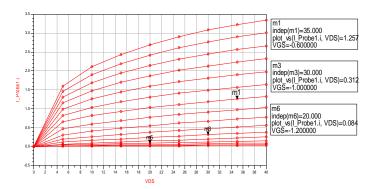

From Figs. 1 (a)-(c), gate to source voltage (Vgs) was chosen -0.6V when drain to source voltage, Vds was chosen 35V.

Fig. 1 (a) Schematic of Transistor Biasing

Abdalla Mohamed Eblabla is with the University of Glasgow. Department of Electronics and Electrical Engineering, Supervisor of Dr. Edward Wisage (e-mail: aeblabla@yahoo.com).

Fig. 1 (b)  $I_{ds}$  vs. Vgs Characteristics for  $V_{ds}$ =35 V

Fig. 1 (c) I<sub>ds</sub> vs. V<sub>ds</sub> Characteristics for Different Vgs Values

#### B. DC-Bias Circuit Design

In lumped elements configuration, DC-block acts as an ideal capacitor used to oppose varieties in voltage while DC-feed acts as an ideal inductor used to oppose varieties in current. Therefore, preventing DC current from affecting the input and output lines is done by DC block while the AC current is allowed to pass throw. DC current is allowed by DC-feed in order to bias the transistor while the AC current is blocked from passing throw [1], [2].

#### C. Output Matching Network

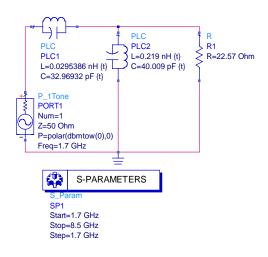

In Fig. 2, output network was done using lumped elements. The first tank was tuned at 5.1 GHz which is the 3rd harmonic frequency (3f<sub>0</sub>). The assumed value of C is 33 pF and calculated value of L is 0.0295 nH.

R<sub>I</sub> can be measured at chosen bias point as following [3]:

$$R_{L} = \frac{V_{1}}{I_{1}} = \frac{\left(\frac{4}{\pi}\right)V_{DD}}{\left(\frac{\pi}{2}\right)I_{dc}} = \frac{8 V_{DD}}{\pi^{2}I_{dc}}$$

$$R_L = (8 \times 35) \div (\pi^2 \times 1.257) = 22.57\Omega$$

#### World Academy of Science, Engineering and Technology International Journal of Electronics and Communication Engineering Vol:7, No:12, 2013

(a)

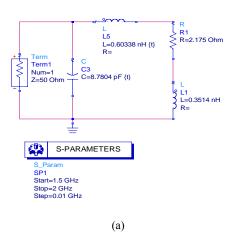

Fig. 2 (a) Schematic of Output Network for Third-Harmonic Peaking Circuit; (b) Output Impedance of the Schismatic

## Input Matching Network

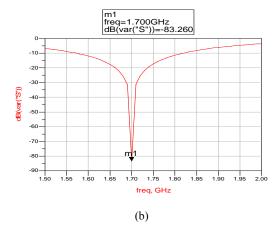

Fig. 3 shows the response of the input matching circuit. It can be seen that the minimum value of the reflection coefficient, -42.138 dB, occurs at 1.7 GHz, which means that the load is matched at that frequency.

Fig. 3 (a) Schematic of Input Matching Network Using Lumped Elements; (b) S-Parameters Output of the Schematic

#### D.Integration of Amplifier Components

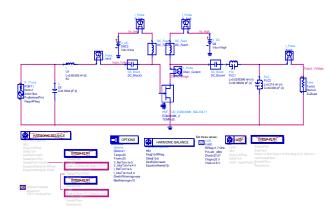

Fig. 4 Schematic of the Lumped Elements Class-F PA Circuit

# E. Simulated Results

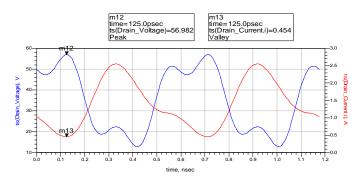

Drain voltage and current waves were achieved in the following figure after running Harmonic Balance (HB) simulation of the three different circuits. This was done with,  $f_0=1.7 GHz$ , Pin=20dBm, Vgs=-0.6V and Vds=35V.

Fig. 5 Simulated (Time Domain) Drain Voltage and Current Waveforms of the Lumped Elements Circuit.

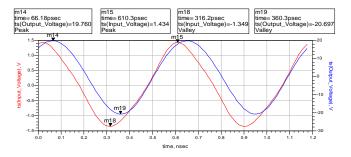

F. Input and Output Voltage Waveforms Simulation Results

Input and output voltage waves were achieved in the following figure after running Harmonic Balance (HB)

#### World Academy of Science, Engineering and Technology International Journal of Electronics and Communication Engineering Vol:7, No:12, 2013

simulation of the three different circuits. This was done with,  $f_0=1.7$ GHz, Pin=20dBm, Vgs=-0.6V and Vds=35V.

Fig. 6 Simulated Input and Output Voltage Waveforms of the Lumped Elements Circuit.

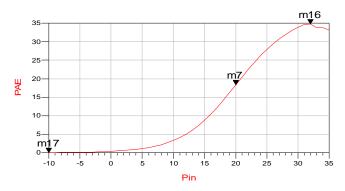

#### G.PAE vs. Pin Simulation Results

The effect of increasing Pin on PAE were achieved in the following figure after running Harmonic Balance (HB) simulation with SWEEP PLAN of the three different circuits. This was done with,  $f_0 = 1.7 \text{GHz}$ , Pin = [-10 to 35dBm], Vgs=-0.6V and Vds=35V.

Fig. 7 PAE(%) vs. Pin(dBm) Simulation Results of the Lumped Elements Circuit.

### II. CONCLUSION

This paper has presented the analysis and design methodology for a Class-F PA. In ADS software, Class-F PA was configured using lumped elements. Maximum output power, gain and power added efficiency of 39.57 dBm, 19.57 dB and 18.38% respectively were obtained by the lumped elements Class-F PA circuit at an operation frequency of 1.7 GHz, an input power of 20 dBm and a bias point of Vds=35 V and Vgs=-0.6 V.

#### III. FUTURE WORK

As mentioned in [6] and [4], a series capacitor and shunt inductor can be included in output network as a compensation circuit in order to absorb the effect of the internal parasitic components of the packaged transistor. This in turn increases the complexity of the output network, but improves the efficiency of Class-F PA.

#### REFERENCES

- Bowick, C., J. Blyler, and C. Ajluni, RF circuit Design, 2rd edition. (Burlington, MA and Oxford, UK: Newnes, 2008), ch. 1.

- [2] Pozar, D.M., Microwave Engineering, 3rd edition. (New York, NY: John Wiley & Sons, 2005), ch. 1.

- [3] Aroshvili, Giorgi, "GaN HEMT and MMIC Design and Evaluation." Master's thesis, University of GÄLE, 2008.

- [4] Ramadan, A., A. Martin, D. Sardin, T. Reveyrand, J-M. Nebus, P. Bouysse, L. Lapierre, J.F. Villemazet and S. Forestier, Study and Design of High Efficiency Switch Mode GaN Power Amplifiers at L-band Frequency, University of Limoges, France, available at http://www.reveyrand.fr/publications/65.pdf (accessed 22 November 2011).

- [5] Modelithics, Datasheet for HMT-EUD-EGN030MK, Rev. 110803 (2011).

- [6] Schhmelzer, David and Stephen I. Long, A GaN HEMT Class F Amplifier at 2 GHz With > 80% PAE, IEEE Journal of Solid-State Circuits 42 no. 10 (2007).