# A Novel Low Power Digitally Controlled Oscillator with Improved linear Operating Range

Nasser Erfani Majd, Mojtaba Lotfizad

**Abstract**—In this paper, an ultra low power and low jitter 12bit CMOS digitally controlled oscillator (DCO) design is presented. Based on a ring oscillator implemented with low power Schmitt trigger based inverters. Simulation of the proposed DCO using 32nm CMOS Predictive Transistor Model (PTM) achieves controllable frequency range of 550MHz~830MHz with a wide linearity and high resolution. Monte Carlo simulation demonstrates that the time-period jitter due to random power supply fluctuation is under 31ps and the power consumption is 0.5677mW at 750MHz with 1.2V power supply and 0.53-ps resolution. The proposed DCO has a good robustness to voltage and temperature variations and better linearity comparing to the conventional design.

*Keywords*—digitally controlled oscillator (DCO), low power, jitter; good linearity, robust

### I. INTRODUCTION

DHASE-LOCKED loops (PLLs) are widely used in many communication systems to clock and data recovery or frequency synthesis [1]. Typical analog PLLs include a phase-frequency detector, a charge pump, a loop filter, a voltage controlled or current controlled oscillator, and a frequency divider [2], [3]. The controlled oscillator is the key component in the core of PLL. Recently, efforts have been made toward the development of fully digital PLLs. Compared to their analog counterparts, fully digital PLLs exhibit better noise immunity and they are invulnerable to DC offset and drift phenomena [4], [5], [6]. Digitally controlled oscillator (DCO) is a replacement of the conventional voltage or current controlled oscillator in the fully digital PLLs. DCO is the heart of the ADPLL that shows higher noise immunity and robustness than the conventional PLLs [1]. DCO dominates the major performances of ADPLL such as power consumption and jitter, and hence is the most important component of such clocking circuits [4], [6], [7]. Since DCO occupies 50% power consumption of an ADPLL [7], the power consumption of DCO should be reduced further to

Nasser Erfani Majd is with the Faculty of Electrical and Computer Engineering, Tarbeat Modares University, Tehran, Iran (phone: +98-21-44338510; fax: +98-21-88220307; email: n.alboghobiesh@modares.ac.ir ), M Lotfiza is with Faculty of Electrical and Computer Engineering

$M. \ Lotfiza \ is \ with \ Faculty \ of \ Electrical \ and \ Computer \ Engineering, \\ Tarbeat \ Modares \ University, \ Tehran, \ Iran \ (e-mail: \ lotfiad@modare.ac.ir \ ).$

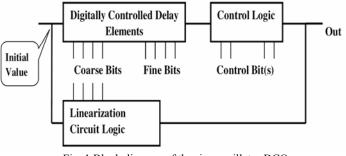

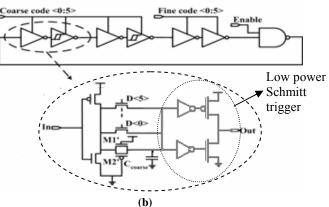

Fig. 1 Block diagram of the ring oscillator DCO

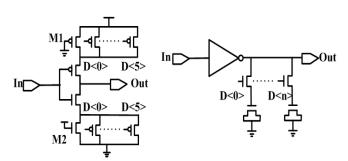

save overall power dissipation to meet low power demands in SOC designs. The Block diagram of the ring oscillator based DCO which is used in this paper is shown in Fig 1. It consists of digitally controlled delay elements which are controlled by coarse and fine bits and a control logic block for enabling DCO and linearization circuit for linearizing the DCO period by increasing the input code. DCO starts to work by applying the initial value to the circuit.Basically, two main techniques exist for designing the DCO as shown in fig. 2. One technique changes the MOS driving strength dynamically using a fixed capacitance loading and achieves a fine resolution [8], [9]. While the other uses shunt capacitor technique to tune the capacitance loading [10], [11]. They both have good linear frequency response and a reasonable frequency operating range. Power consumption is an important problem for portable battery charged computing systems, so the reduction of the power consumption has become a major concern.A simple DCO that directly uses an inverter ring is presented in [12], but has insufficient resolution for most appli

Fig. 2 Standard Cell of Digitally controlled oscillator. (a) Driving strength controlled. (b) Shunt capacitance controlled.

applications. Another DCO example consists of bank of tristate inverter buffers [13]. The delay resolution in this case can be controlled by the number of enable buffers. However, [13] has the disadvantages of large silicon area and high power consumption. Another means of fine resolution enhancement, implemented by an Or-And-Inverter (OAI) cell shunted with two tri-state inverters to enhance driving capability, was proposed in [3]. The proposed DCO in [3] has less area and power consumption than [13]. However, the resolution step of the proposed DCO is nonuniform and sensitive to power-supply variation because it uses OAI cell to change the delay resolution, this technique also requires an additional decoder for mapping OAI cell control input. This paper presents a low power, low jitter and high resolution DCO using binary controlled pass transistors and low power Schmitt trigger. The DCO is designed using the 32nm CMOS Predictive Transistor Model (PTM) and HSPICE simulator.

#### II. CONVENTIONAL AND PROPOSED DCO ARCHITECTURE

DCO should generate an oscillation period of  $T_{DCO}$ , which is a function of digital input word D and given by:

$$T_{DCO} = f(d_{n-1}2^{n-1} + d_{n-2}2^{n-2} + \dots + d_12^1 + d_02^0)$$

(1)

the DCO transfer function is defined such that the period of oscillation  $T_{DCO}$  is linearly proportional to digital word D with an offset

$$T_{DCO} = T_{offset} - D.T_{step}$$

D:Digital control bits (2)

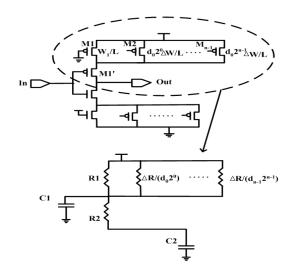

where  $T_{offset}$  is a constant offset period and  $T_{step}$  is the period of quantization step. For the conventional driving strength controlled DCO shown in Fig. 3, the delay tuning range of this standard cell is obtained as follows:

$$\frac{T_{\text{une}}}{2} = (C_1 - C_2)(R_1 \| \frac{\Delta R}{d_0} \| \frac{\Delta R}{d_1 2} \| \dots \| \frac{\Delta R}{d_{n-1} 2^{n-1}}) - (C_1 + C_2)R_1 \quad (3)$$

$$=\frac{R_{1}(C_{1}+C_{2})}{1+(D_{1}\Delta W)/W_{1}}-(C_{1}-C_{2})R_{1}$$

(4)

$$\approx R_1(C_1 + C_2) \frac{D.\Delta W}{W_1}, \quad (Only if \frac{D.\Delta W}{W_1} \square 1)$$

(5)

where  $R_1$  is the equivalent resistance of M1 and W1 is the width of M1. In order to have a good linear tuning range, the width of transistor M1 has to be increased as can be seen in Equation (5). Consequently, the equivalent resistance  $R_1$  will decrease resulting in a smaller delay tuning range. One way to increase the tuning range while keeping the linear response is to increase the capacitance loading. However this will minimize the maximum frequency that the DCO can accomplish and the power consumption will also be increased.

Fig. 3 Equivalent circuit for the calculation of delay tuning range

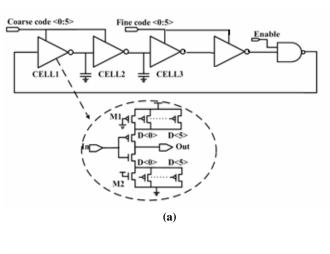

The proposed DCO is based on ring oscillator implemented with low power Schmitt trigger based inverters. It uses binary controlled pass transistor arrays to control the period of DCO. Schmitt trigger based inverter has a higher low to high switching threshold and lower high to low switching threshold compared to the conventional As a result, the proposed DCO circuit provides the same tuning range with smaller capacitance loading, which is beneficial for power consumption reduction [15]. Moreover, in conventional DCO circuit, the slope of the input signal to each stage decreases gradually due to the large delay between each stage. This result in not only non-ideal rail-to-rail switch but also a poor power performance. The steep slope of the output signal from the Schmitt trigger based inverter minimizes this problem to certain extend. The improved DCO has two coarse delay cells and two fine delay cells and a NAND gate for reset. We don't use the Schmitt trigger in fine delay cells of DCO, because Schmitt trigger transistors are switched in each cycle, so they themselves consume a lot of power in the DCO therefore omission of Schmitt trigger from fine delay cells can decrease the power consumption of the circuit. Since fine delay cells of DCO do not have a capacitance loading thus fine delay cells output signal is still sharp and omission of the Schmitt trigger from fine delay cells does not disturb the DCO performance. Furthermore we use the low power Schmitt trigger in coarse delay cells which has two inverters in its structure and these inverters act as buffers in the signal path and by reconstructing the signal, reduce the jitter of the DCO. This Schmitt trigger is reported in [14]. The high to low and low to high switching threshold of the Schmitt trigger is obtained as follows

$$V_{TR} = \frac{V_{tn} + \sqrt{K_n / K_p} (VDD - V_{tp)}}{1 + \sqrt{(\frac{K_n}{K_p})}}$$

(6)

Where Kn and Kp are the transconductance factors of  $Mn_{inv}$  and  $Mp_{inv}$ , and Vtn and Vtp are their respective threshold voltages. The circuit diagrams of the conventional DCO and proposed DCO are showed in Fig. 4. In order to compare the power consumption, both circuits must be equally sized.

### III. COMPARISON OF POWER CONSUMPTION BETWEEN THE CONVENTIONAL AND PROPOSED DCO STRUCTURES

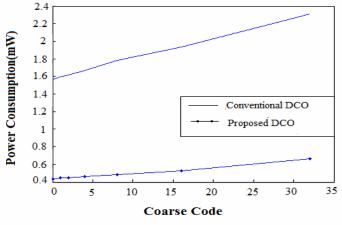

Two structures of DCO are simulated and compared using 32nm CMOS PTM (Predictive Transistor Model) with a supply voltage of 1.2Volts and HSPICE simulator. The impact of each control bit on the period of the two DCO structures is shown in table 1. Both structures have the same linear tuning range until 5<sup>th</sup> bit is asserted. This is due to the fact that the requirement for linear tuning range fails when large comparing to W1 so these DAW becomes too structures are linear for the first 32 input coarse codes. In order to compare the power consumption, the first 5 control bits are chosen instead of 6, since the last control bits contributes to non-linear tuning range which is not desired for DCO. Moreover, since two DCO structures have the same operation ranges, it is more reasonable for us to compare their power consumption. Compared to the conventional DCO, the

Fig. 4 Digitally Controlled Oscillator. (a) Conventional DCO structure, (b) proposed DCO structure

Fig. 5 Power consumption of the two DCO structures

proposed DCO saves approximately 70% power consumption as shown in fig 5. As discussed in section II, this reduction is due to the comparatively smaller capacitance loading for the Schmitt trigger based inverter than the conventional inverter at the same operating frequency and using the low power Schmitt trigger in the inverters of coarse delay cells. The proposed DCO is more power efficient than the conventional DCO.

TABLE I IMPACT OF EACH CONTROL BIT ON THE DCO PERIOD

| Control bits | Conventional DCO |               | Proposed DCO   |               |  |  |  |  |  |  |

|--------------|------------------|---------------|----------------|---------------|--|--|--|--|--|--|

|              | Period<br>(ns)   | Delta<br>(ps) | Period<br>(ns) | Delta<br>(ps) |  |  |  |  |  |  |

| 100000       | 1.1905           | 246.7         | 1.1902         | 242.8         |  |  |  |  |  |  |

| 010000       | 1.4372           | 124.5         | 1.4330         | 134.8         |  |  |  |  |  |  |

| 001000       | 1.5617           | 84.5          | 1.5678         | 91.6          |  |  |  |  |  |  |

| 000100       | 1.6462           | 42            | 1.6594         | 32.7          |  |  |  |  |  |  |

| 000010       | 1.6882           | 20.1          | 1.6921         | 18.1          |  |  |  |  |  |  |

| 000001       | 1.7083           | 21.9          | 1.7102         | 19.9          |  |  |  |  |  |  |

| 000000       | 1.7302           | -             | 1.7301         | -             |  |  |  |  |  |  |

## IV. IMPROVING LINEAR OPERATING RANGE OF THE PROPOSED DCO AND SIMULATION RESULTS

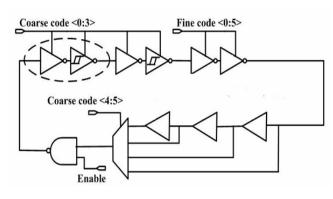

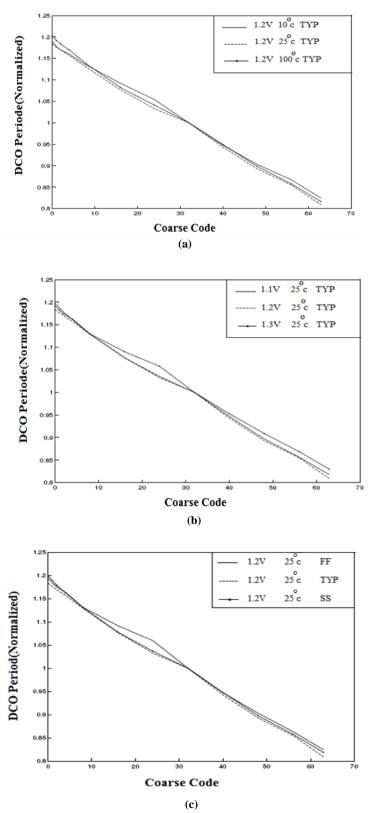

The proposed DCO which is explained in section II has a limited linear operating range as discussed above. In this paper, three stage constant delay chains and 4:1 multiplexer are used to increase the operating range [15], the proposed DCO and its linearization circuit are shown in Fig. 6. The 6<sup>th</sup> bit is taken off for better linear response and the 1<sup>st</sup> bit is also taken off for larger coarse resolution. So this structure is linear for 64 input coarse codes instead of 32 input coarse codes. The proposed DCO structure with increased operating range is designed and simulated using 32nm CMOS PTM model and HSPICE simulator. The frequency ranges of the coarse and fine tuning loops are shown in Fig. 7. The curves have a good linearity which is a key factor of the PLL performance. The operational frequency response to the process, temperature and voltage variations are shown in Fig. 8. The curves show the normalized data with respect to

### World Academy of Science, Engineering and Technology International Journal of Electrical and Computer Engineering Vol:5, No:3, 2011

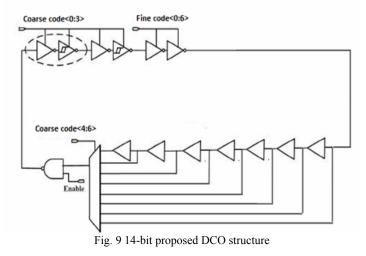

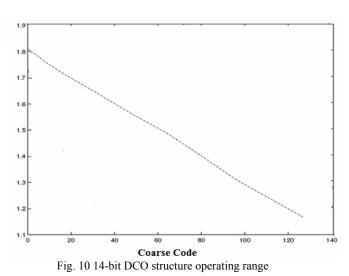

the center frequency. Fig. 8 shows that the relative delay per code is almost the same regardless of the process, temperature and voltage variations, which means this DCO design is robust to PVT variations. We can extend the linearization circuit to achieve a 14-bit DCO which is linear for 128 input coarse codes. Extended linearization circuit is shown in Fig. 9. It consists of a seven stage constant delay chain and 8:1 Mux. The 7<sup>th</sup> and 6<sup>th</sup> bits are taken off for better linear response and 1<sup>st</sup> bit is also taken off for better coarse resolution. The simulation results show that the DCO curve has a good linearity. The frequency ranges of the coarse tuning loop are shown in Fig. 10.

Fig. 6 The proposed DCO structure with improved linear operating range

Fig. 7 Operating range of the proposed DCO. (a) Coarse loop (b) Fine loop

Fig. 8 Delay characteristics of the coarse loop according to Process, Voltage and Temperature variations. (a) Temperature Variation, (b) Voltage Variation, (c) Process Variation

### World Academy of Science, Engineering and Technology International Journal of Electrical and Computer Engineering Vol:5, No:3, 2011

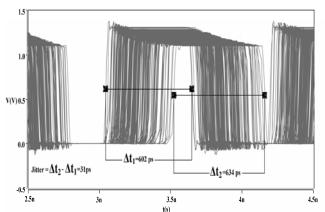

The time-period jitter is the time difference between the measured cycle period and the ideal cycle period. The jitter performance of the proposed DCO is simulated by Monte Carlo analysis using a Gaussian distribution function taking into account 10% variation in supply voltage. The results are shown in Fig. 11 by overlapping every cycle period. A 31ps time-period Jitter is measured.

Table 3 shows the measurement results to compare with a few recent state-of-the-arts DCO designs [1], [4], [10], [13].

Fig. 11 Time-period jitter of the proposed DCO (Monte Carlo analysis)

| TADLE II                           |                    |            |  |  |  |  |  |

|------------------------------------|--------------------|------------|--|--|--|--|--|

| CHARACTERISTIC OF THE PROPOSED DCO |                    |            |  |  |  |  |  |

| Items                              | Coarse delay       | Fine delay |  |  |  |  |  |

| Resolution                         | 6 bit              | 6bit       |  |  |  |  |  |

| Max. DCO Gain                      | 13ps               | 0.53ps     |  |  |  |  |  |

| Avg. DCO Gain                      | 9ps                | 0.25ps     |  |  |  |  |  |

| Operation range                    | 550~830 MHz        |            |  |  |  |  |  |

| Power consumption                  | 0.5677mW @ 750 MHz |            |  |  |  |  |  |

TABLE II

The proposed DCO achieves the finest LSB resolution and the highest operating frequency. In addition, the proposed DCO consumes less power than the others.

### V. CONCLUSION

A low power 12 bit digitally controlled CMOS oscillator (DCO) design for low power consumption and low jitter is presented. The presented DCO demonstrate a good robustness to process, voltage and temperature variations and better linearity comparing to the conventional design. Simulation of the proposed DCOs using 32 nm CMOS Predictive Transistor Model and HSPICE simulator achieves a frequency of 550~830 MHz and power consumption of 0.5677mW at 750 MHz and 1.2V power supply. The performance, flexibility, and robustness make the proposed DCO viable for high performance fully digital PLL application.

| COMPARISON WITH EXISTING DCOS. |                  |                  |                     |                    |                     |  |  |  |

|--------------------------------|------------------|------------------|---------------------|--------------------|---------------------|--|--|--|

| Function                       | [13]             | [1]              | [4]                 | [10]               | Proposed<br>DCO     |  |  |  |

| Process                        | 0.6 um @<br>5V   | 0.35um @<br>3.3V | 0.35 um @<br>3.3V   | 0.13 um @<br>1.65V | 32nm@ 1.2V          |  |  |  |

| DCO control<br>word length     | 10 bits          | 15 bits          | 12 bits             | 8bits              | 12 bits             |  |  |  |

| Coarse<br>Resolution           | 550 ps           | 385 ps           | 300 ps              | -                  | 12 ps               |  |  |  |

| LSB(Fine)<br>Resolution        | 10 ps            | 1.55 ps          | 5ps                 | 40 ps              | 0.53 ps             |  |  |  |

| DCO output<br>frequency        | 10~12.5<br>(MHz) | 18~214<br>(MHz)  | 45~450<br>(MHz)     | 150(MHz)           | 550~830<br>(MHz)    |  |  |  |

| Power consumption              | 164mW@<br>100MHz | 18mW@<br>200MHz  | 100 mW @<br>450 MHz | 1mW @<br>150MHz    | 0.5677mW@<br>750MHz |  |  |  |

TABLE III

#### REFERENCES

- [1] P.-L. Chen, C.-C. Chung, and C.-Y. Lee, "A portable digitally controlled oscillator using novel varactors," *IEEE Transactions on* Circuits and Systems II, vol. 52, no. 5, pp. 233-237, 2005.

- Roland E. Best: "Phase-locked loops. Theory, Design, and applications," McGraw-Hill Book Company, 1984.

B. Razavi, "Monolithic Phase-Locked Loops and Clock-Recovery [2]

- [3] Circuits," IEEE Press, 1996. Collection of IEEE PLL papers.

- C. Chung and C. Lee, "An all-digital phase-locked loop for high-speed [4] clock generation," IEEE J. Solid-State Circuits, vol. 38, pp. 347-351, Feb. 2003.

- P. Nilsson and M. Torkelson, "A monolithic digital [5] clock-generator for on-chip clocking of custom DSP's," IEEE J. Solid-State Circuits, vol.31, pp. 700-706, May 1996.

- J. Dunning, G. Garcia, J. Lundberg, and E. Nuckolls, "An all-digital [6] phase-locked loop with 50-cycle lock time suitable for high performance microprocessors," IEEE J. Solid-State Circuits, vol. 30, pp. 412-422, Apr. 1995.

- [7] T.Olsson and P.nilsson, "A digitally controlled PLL for SoC application," IEEE j. Solid-state Circuits, Vol.39, no. 5,pp.751-760, May 2004.

- R. B. Staszewski and P. T. Balsar, " Phase-Domain All-Digital Phase-[8] Locked Loop,"IEEE Trans. Circuits and Systems II, Vol. 52, pp. 159-163, Mar. 2005.

- M. Saint-Laurent et al, "A Digitally Controlled Oscillator Constructed [9] Using Adjustable Resistor," IEEE Southwest Symposium on Mixed-Signal Design, 2001.

- [10] P. Raha, S. Randall, R. Jennings, B. Helmick, A. Amerasekera, and B.Haroun, "A robust digital delay line architecture in a 0.13-\_m CMOS technology node for reduced design and process sensitivities," in Proc. ISQED'02, pp. 148-153, Mar. 2002.

- [11] P. Andreani, F. Bigongiari, R Roncella, R. Saletti and P.Tenini, "A Digitally Controlled Shunt Capacitor CMOS Delay Line," Analog Circuits and Signal Processing, Kluwer Academic Publishers, Volume 18, pp. 89-96. 1999.

- [12] T. Olsson and P. Nilsson, "Portable digital clock generator for digital signal processing applications," Electron. Lett., vol. 39, pp. 1372-1374, Sep. 2003.

- [13] E. Roth, M. Thalmann, N. Felber, and W. Fichtner, "A delay-line based DCO for multimedia applications using digital standard cells only," in Dig. Tech. Papers ISSCC'03, Feb. 2003, pp. 432-433.

- V.A. Pedroni," Low-voltage high-speed Schmitt trigger and compact [14] window comparator," Electronics Letters, vol. 41 no. 22, Oct 2005.