# Investigation of Inter Feeder Power Flow Regulator: Load Sharing Mode

Ahmed Hossam-Eldin

Ahmed Elserougi Ahmed Massoud

Shehab Ahmed

Electrical Engineering Department Alexandria university, Egypt hossamudn@hotmail.com abbas\_zone@yahoo.com Electrical and computer Engineering Dept. Qatar university, Qatar

Qatar university, Qatar ahmed.massoud@qu.edu.qa Elect. and computer Engineering Dept. Texas A&M University at Qatar, Qatar shehab.ahmed @qatar.tamu.edu

**Abstract**—The Inter feeder Power Flow Regulator (IFPFR) proposed in this paper consists of several voltage source inverters with common dc bus; each inverter is connected in series with one of different independent distribution feeders in the power system. This paper is concerned with how to transfer power between the feeders for load sharing purpose. The power controller of each inverter injects the power (for sending feeder) or absorbs the power (for receiving feeder) via injecting suitable voltage; this voltage injection is simulated by voltage drop across series virtual impedance, the impedance value is selected to achieve the concept of power exchange between the feeders without perturbing the load voltage magnitude of each feeder. In this paper a new control scheme for load sharing using IFPFR is proposed.

Keywords-IFPFR, Load sharing, Power transfer

## I. INTRODUCTION

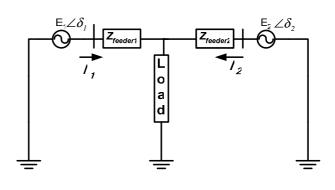

N general, the droop technique [1] has been widely used as a load-sharing scheme in conventional power system with multiple generators. In this droop method, the generators share the system load by dropping the frequency of each generator with the real power delivered by the generator. This allows each generator to share changes in total load in a manner determined by its frequency droop characteristic and essentially utilizes the system frequency as a communication link between the generator control systems. Similarly, a droop in the voltage amplitude  $V_{max}$  with reactive power is used to ensure reactive power sharing. This load sharing technique is based on the power flow concept in an ac transmission system, which states that the flow of the active power and reactive power between two sources can be controlled by adjusting the power angle and the voltage magnitude respectively. This concept is explained in Fig. 1. Fig. 1 shows two voltage sources connected to a load through feeder impedance. The real power flow is mostly influenced by the power angles  $\delta_1$ and  $\delta_2$ , while the reactive power flow depends on the voltages  $E_1$  and  $E_2$  [1].

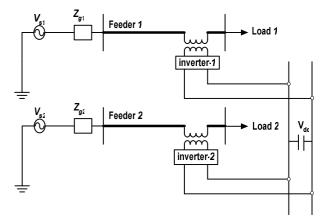

A new proposed technique for load sharing using the Inter feeder Power Flow Regulator (IFPFR) is proposed in this paper. The IFPFR consists of several voltage source inverters connected to different distribution feeders in the power system with common dc bus; Fig. 2 shows the inter feeder power flow regulator with two radial independent feeders. The voltage source converter (VSC) is connected in series with the grid. The IFPFR can be used as inter-line dynamic voltage restorer IDVR [2-5], in this mode of operation, the basic operating principle of the inverter is to inject an appropriate voltage in series with the supply through injection transformer whenever voltage sags or swells take place. A new mode of operation is introduced in this paper; it is the power transfer mode. This mode of operation allows transferring power between feeders for load sharing purpose.

Fig. 1.Two sources connected to a load

Fig. 2.Inter feeder power flow regulator (IFPFR) for two feeder

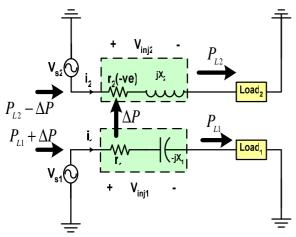

Fig. 3.Inter feeder power flow regulator with two radial independent feeders

# II. POWER CONTROLLER WITH VIRTUAL IMPEDANCE INJECTION FOR SENDING FEEDER

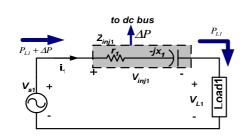

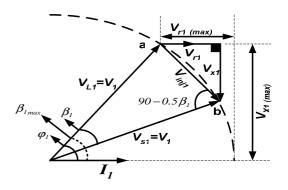

For inter feeder power flow regulator with two radial independent feeders, if it is desired to transfer power from feeder 1 (sending feeder) to feeder 2 (receiving feeder) as shown in Fig.3. The inverter 1 will be responsible for pumping the required power to the dc bus via injecting suitable virtual impedance. Assuming that the feeder is feeding a three phase balanced load, Fig. 4 shows per phase equivalent circuit of feeder 1 with series virtual impedance injection. Fig. 5 shows the corresponding phasor diagram. Since the three phase load is balanced, all the following analysis will be done for per phase circuit. The voltage injection is simulated by a voltage drop across series impedance. The impedance injection must not perturb the load voltage magnitude. Moreover, the power consumed by this impedance represents the required power to be transferred. To transfer power and to keep the load voltage magnitude unchanged, the injected voltage must have two components, namely  $V_{rI}$  which is in phase with current phasor, and  $V_{xl}$ , which is perpendicular to the current phasor, as shown in Fig. 5. The  $V_{rl}$  component absorbs active power from source  $(\Delta P)$  and  $V_{xl}$  component keeps the load voltage magnitude unchanged. For a given transferred power  $\Delta P$ , the corresponding value for the capacitive reactance  $x_1$  should be estimated from the following relations to ensure constant load voltage magnitude. The load power is given by (1)

$$P_{Ll} = I_l V_l \cos(\varphi_l). \tag{1}$$

Fig. 4 Feeder 1 circuit with virtual impedance injection

Fig. 5 Phasor diagram of feeder 1

The supply power is given by (2), as indicated in the phasor diagram shown in Fig. 5.

$$P_{LI} + \Delta P = I_I V_I \cos(\varphi_I - \beta_I)$$

<sup>(2)</sup>

Hence

$$\beta_{I} = \varphi_{I} - \cos^{-1}\left(\frac{P_{LI} + \Delta P}{I_{I}V_{I}}\right)$$

(3)

The maximum value for angle  $\beta$  is the load power factor angle  $\varphi_i$  where the supply input power factor will be unity. Moreover, the maximum allowable  $\Delta P$  corresponds to unity input power factor. For a given load power factor, the maximum value for  $\Delta P$  is given by (4)

$$\Delta P_{max} = I_1 V_1 (1 - \cos(\varphi_1)) \tag{4}$$

The resistance  $r_i$ , which represents absorbed active power from feeder, is given by

$$r_{I} = \frac{\Delta P}{I_{I}^{2}} = \frac{I_{I} V_{I} \left( \cos(\varphi_{I} - \beta_{I}) - \cos(\varphi_{I}) \right)}{I_{I}^{2}}$$

(5)

From the phasor diagram, shown in Fig. 5, the chord *ab* length is given by

$$chord(ab) = 2V_{I} sin(0.5\beta_{I}) = \sqrt{Vr_{I}^{2} + Vx_{I}^{2}}$$

(6)

Hence, the capacitive reactance  $x_1$  can be calculated as

$$x_{I} = \sqrt{\frac{(ab^{2} - Vr_{I}^{2})}{I_{I}^{2}}}$$

(7)

Substituting (6) in (7), yields

$$x_{I} = \sqrt{\left(4\frac{V_{I}^{2}}{I_{I}^{2}}\sin^{2}(0.5\beta_{I}) - r_{I}^{2}\right)}$$

(8)

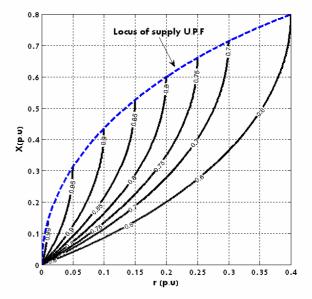

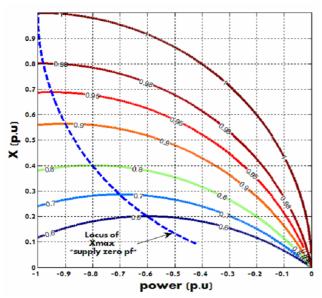

Fig. 6 shows the relation between  $\Delta P$  (i.e.  $r_1$ ) and  $x_1$  for different values of load power factor assuming V<sub>1</sub>=1p.u, Z<sub>1load</sub>=1p.u with respect to the feeder 1 base values.

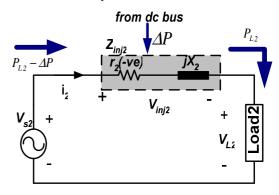

# IV. POWER CONTROLLER WITH VIRTUAL IMPEDANCE INJECTION FOR RECEIVING FEEDER

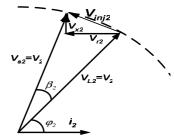

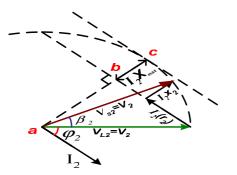

The inverter 2 will be responsible for absorbing the transferred power via injecting suitable virtual impedance Fig. 7 shows per phase equivalent circuit of feeder 2 with series virtual impedance injection. Fig. 8 shows the corresponding phasor diagram. The voltage injection is simulated by a voltage drop across series impedance. The impedance injection must not perturb the load voltage magnitude. Moreover, the power generated by this impedance represents the absorbed power.

For each received power  $\Delta P$ , inductive reactance  $x_2$  should be estimated from the following relations to guarantee keeping the voltage magnitude unchanged. The load power is given by (9)

$$P_{L2} = I_2 V_2 \cos(\varphi_2).$$

(9)

The supply power is given by (10), as indicated in the phasor diagram shown in Fig. 8.

$$P_{L2} - \Delta P = I_2 V_2 \cos(\varphi_2 + \beta_2)$$

(10)

$$\beta_2 = -\varphi_2 + \cos^{-l}(\frac{P_{L2} - \Delta P}{I_2 V_2})$$

(11)

The resistance  $r_2$ , which represents received active power, is given by

$$r_{2} = \frac{-\Delta P}{I_{2}^{2}} = \frac{I_{2}V_{2}(\cos(\varphi_{2} + \beta_{2}) - \cos(\varphi_{2}))}{I_{2}^{2}}$$

(12)

From the phasor diagram, shown in Fig. 8, the chord *ab* length is given by

$$chord(ab) = 2V_2 \sin(0.5\beta_2) = \sqrt{Vr_2^2 + Vx_2^2}$$

(13)

Hence, the inductive reactance  $x_2$  can be calculated as

$$E_2 = \sqrt{\frac{(ab^2 - Vr_2^2)}{I_2^2}}$$

(14)

Substituting (13) in (14), yields

λ

$$x_{2} = \sqrt{\left(4\frac{V_{2}}{I_{2}^{2}} sin^{2}(0.5\beta_{2}) - r_{2}^{2}\right)}$$

(15)

Fig. 6 Relation between  $\Delta P$  (or  $r_1$ ) and  $x_1$  for different values of load power factor

Fig. 7 Feeder 2 circuit with virtual impedance injection

Fig. 8.Phasor diagram of feeder 2

Fig. 9 shows the relation between  $\Delta P$  and  $x_2$  for different values of load power factor assuming V<sub>2</sub>=1p.u, Z<sub>2load</sub>=1p.u with respect to the feeder 2 base values. In Fig. 9, for certain load power factor as the received power increases the inductive reactance increases even locus of  $X_{max}$  after that inductive reactance decreases as the received power increases. It can be illustrated from the phasor diagram shown in Fig. 10 as

follows, as the length of  $I_2(r_2)$  term increases the term  $I_2(x_2)$  increases even reach maximum length this happens when the  $V_{s2}$  phasor is perpendicular to  $I_2$  phasor i.e. zero input power factor, i.e. the supply out zero power, and all received power fed to the load. In this case if power command ( $\Delta P$ ) increased the received power will fed both the load and the source. In case of  $X_{max}$ , the angle  $\beta$  is given by (16)

$$\beta_2 = 90^\circ - \varphi_2 \tag{16}$$

The value of  $X_{max}$  is given by (17), as indicated in the phasor diagram shown in Fig. 10.

$$X_{max} = \frac{bc}{I_2} = \frac{ac - ab}{I_2} = \frac{V_2 - V_2 \sin(\varphi_2)}{I_2}$$

(17)

Hence the per unit value of  $X_{max}$  is given by (18)

$$X_{max}(p.u) = l - sin(\varphi_2)$$

(18)

Fig. 9 Relation between transmitted power (i.e.  $r_2$ ) and  $x_2$  for different load power factor

If a load of 0.8 lag power factor connected to the feeder 2, the  $X_{max}$  from (18) will equal to (1-0.6=0.4 p.u). This result is similar to the data of graph shown in Fig. 9. At this case the received power=0.8 p.u and the load power=0.8 p.u, that means the supply out zero power; i.e. zero input power factor.

Fig. 10 Phasor diagram of the receiving feeder

### III. PROPOSED CONTROL SCHEME

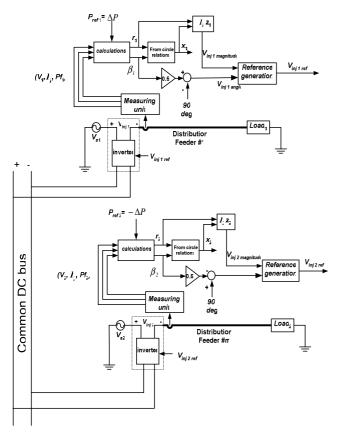

For each feeder if the angle of voltage phasor  $V_s$  is assumed zero. For given  $\Delta P$  and measured signals (*I*, *V*, *pf*) a voltage source inverter is used to inject a suitable voltage in series with the grid; this injected voltage has a reference magnitude is equal to  $(I_{.}\sqrt{r^2 + x^2})$  where *r*, *x* calculated from Eqs (5), (8) for the sending feeder, but for the receiving feeder Eqs (12), (15) can be used. The phasor of the injected voltage for feeder 1 will lag the V<sub>s1</sub> phasor by 90°-0.5 $\beta$  as shown in Fig. 5, but the phasor of the injected voltage for feeder 2 will lead the V<sub>s2</sub> phasor by 90°-0.5 $\beta$  as shown in Fig. 10.The control block diagram of the IFPFR when power transfer mode is applied is shown in Fig. 11.

## IV. CASE STUDIES

*Case 1;* for inter feeder power flow regulator with two radial independent feeders in low voltage distribution system, it is desired to transfer power equal to 0.1p.u from feeder 1 to feeder 2 for 0.1 < t < 0.8s. Assume same base values for both feeders, the system data is tabulated in table I. The simulation results are shown in Fig. 12a, 12b.

| TABLE I CASE 2 DATA |                                 |

|---------------------|---------------------------------|

| V <sub>s1</sub>     | 1 p.u                           |

| V <sub>s2</sub>     | 1 p.u                           |

| Load1               | 1 p.u impedance with 0.8 pf lag |

| Load2               | 1 p.u impedance with 0.8 pf lag |

The inverter 1 will be responsible for pumping the required power the dc bus via injecting suitable virtual impedance which equal to  $(r_1 \cdot jx_1)$  where  $r_1=0.1$ ,  $x_1=0.1641$  p.u. In the other hand, the inverter 2 will be responsible for absorbing the transferred power via injecting suitable virtual impedance which equal to  $(r_2+jx_2)$  where  $r_2=-0.1$ ,  $x_2=0.1141$  p.u. From Fig. 12a, the power transfer is achieved without perturbing the load voltage magnitude at each feeder. The supply power  $P_{s1}$ increased when load sharing mode is applied, however load power  $P_{Load1}$  did not change, the difference between  $P_{s1}$  and  $P_{Load1}$  is fed to the dc bus via injecting  $V_{inj1}$ , The interaction between this injected voltage the feeder current  $I_1$  produces the power to be transferred to the other feeder.

### World Academy of Science, Engineering and Technology International Journal of Electrical and Computer Engineering Vol:4, No:9, 2010

Fig. 11 Control of IFPFR under load sharing mode

Fig. 12a Time response of sending feeder variables for case 1; all in p.u values

Fig. 12b Time response of receiving feeder variables for case 1; all in p.u values

However from Fig. 12b, the supply power  $P_{s2}$  decreased when load sharing mode is applied, however load power  $P_{Load2}$  did not change, the difference between  $P_{Load2}$  and  $P_{s2}$  is absorbed from the dc bus via injecting  $V_{inj2}$ , The interaction between this injected voltage the feeder current  $I_2$  produces the power to be received from the other feeder.

*Case 2*; for inter feeder power flow regulator with two radial independent feeders, it is desired to transfer power equal to 0.1p.u from feeder 1 to feeder 2. Assume same base values for both feeders, the system data is tabulated in table II. The time response of the sending feeder variables is shown in Fig. 13.

| TABLE II CASE 2 DATA |                                                                  |

|----------------------|------------------------------------------------------------------|

| V <sub>s1</sub>      | =1 p.u                                                           |

| V <sub>s2</sub>      | =1 p.u                                                           |

| Load1                | =1 p.u impedance with 0.8 pf lag for 0 <t<0.6s< th=""></t<0.6s<> |

|                      | and                                                              |

|                      | =1.1 p.u impedance with 0.7pf lag for t>0.6s                     |

| Load2                | =1 p.u impedance with 0.8 pf lag                                 |

In this case the inverter 1 will be responsible for pumping the required power the dc bus via injecting suitable virtual impedance which equal to  $(r_I ext{-} j x_I)$  where  $r_I ext{=} 0.1$ ,  $x_I ext{=} 0.1641$  p.u for 0<t<0.6s and  $r_I ext{=} 0.1219$ ,  $x_I ext{=} 0.2087$  p.u for t>0.6s. The impedance value is changed because the feeder current changed at t=0.5s with constant required power  $\Delta P$ . In the other hand, the inverter 2 will be responsible for absorbing the transferred power via injecting suitable virtual impedance which equal to  $(r_2+jx_2)$  where  $r_2=-0.1$ ,  $x_2=0.1141$  p.u.

Fig. 13 Time response of sending feeder variables for case 2; all in p.u values

#### V. CONCLUSION

A new proposed technique for load sharing using the IFPFR is proposed in this paper. One of the inverters will be responsible for pumping the required power to the dc bus via injecting suitable virtual positive resistance in series with virtual capacitor through its feeder. The other inverter will be responsible for absorbing the transferred power via injecting virtual negative resistance in series with virtual inductor through its feeder. The power will transfer from one feeder to another without perturbing the load voltage magnitude in each feeder. The proposed load sharing technique is simulated using MATLAB/SIMULINK to check its validity, and the simulation output was satisfactory.

#### REFERENCES

- Mohammad N. Marwali, Jin-Woo Jung and Ali Keyhani, "Control of Distributed Generation Systems—Part II: Load Sharing Control," IEEE transaction on power electronics, vol. 19 no. 6, Nov 2004.

- [2] S. S. Choi, B. H. Li, and D. M. Vilathgamuwa, "Dynamic voltage restoration with minimum energy injection," IEEE Trans. Power System, vol. 15, no. 1, pp. 51–57, Feb. 2000.

- [3] Vilathgamuwa, D.M.; Wijekoon, H.M.and Choi S.S, "Interline dynamic voltage restorer: a novel and economical approach for multiline power quality compensation," Industry Applications Conference, 2003. 38th IAS Annual Meeting, pp. 833 - 840 vol.2.

- [4] Wijekoon, H.M.; Vilathgamuwa, D.M.; Choi, S.S.," Interline dynamic voltage restorer: an economical way to improve interline power quality," Generation, Transmission and Distribution, 2003, IEE Proceedings, Vol. 150, Issue 5, pp. 513 – 520.

- [5] D. Mahinda, H. M. Wijekoon, and S. S. Choi, "A Novel Technique to Compensate Voltage Sags in Multi-line Distribution System the Interline Dynamic Voltage Restorer," IEEE transactions on industrial