# Performance Comparison and Analysis of Serial Concatenated Convolutional Codes

Dongwon Lee, and Eon Kyeong Joo, Member, IEEE

**Abstract**—In this paper, the performance of three types of serial concatenated convolutional codes (SCCC) is compared and analyzed in additive white Gaussian noise (AWGN) channel. In Type I, only the parity bits of outer encoder are passed to inner encoder. In Type II and Type III, both the information bits and the parity bits of outer encoder are transferred to inner encoder. As results of simulation, Type I shows the best bit error rate (BER) performance at low signal-to-noise ratio (SNR). On the other hand, Type III shows the best BER performance at high SNR in AWGN channel. The simulation results are analyzed using the distance spectrum.

Keywords—Distance spectrum, MAP algorithm, SCCC.

# I. INTRODUCTION

THE parallel concatenated convolutional codes (PCCC) [1] which was proposed by Berrou *et al.* in 1993 shows the excellent error correction performance by iterative decoding. For example, if the interleaver size is more than 10,000 bits and the number of iterations is more than five, it is shown to have the performance within 0.5dB of the Shannon limit around the bit error rate (BER) of 10<sup>-5</sup>. However, PCCC has the error floor problem, which is the flattening of BER at high signal-to-noise ratio (SNR) due to a small number of low weight codewords [2].

As one of the methods to avoid the error floor of PCCC, serial concatenated convolutional codes (SCCC) [3] was proposed by Benedetto *et al.* in 1996. While the only information bits of the first component encoder are passed to the second encoder through an interleaver in PCCC, the parity bits of outer encoder are transferred to inner encoder through an interleaver and the transfer of the information bits is optional in SCCC. In general, the MAP (maximum *a posteriori*) algorithm [4], [5] is used in the decoder of concatenated convolutional codes. The log-likelihood ratio (LLR) for parity bits is essentially calculated in the decoder of SCCC and that for information bits might be required according to the encoder type.

The BER performance of SCCC is varied according to constituent codes, interleaver type and size, and concatenation

Manuscript received September 1, 2006; revised October 11, 2006.

D. Lee is with Samsung Electronics, san #24 Nongseo-dong, Giheung-gu, Yongin-si, Gyeonggi-do 446-711, Korea (phone: 82-31-209-0822; fax: 82-31-209-0837; e-mail: leespace1@hanmail.net).

E. K. Joo is with the School of Electronic and Electrical Engineering, Kyungpook National University, Daegu 702-701, Korea.

method [6], [7]. The variation due to constituent codes and interleavers has been researched in other papers, but it is not yet for the concatenation method. Therefore, in this paper, the BER performance of three types of SCCC with different concatenation scheme is compared and analyzed in additive white Gaussian noise (AWGN) channel. The distance spectra of the three types are used to analyze the performance.

This paper is organized as follows. Section II describes the encoder and the decoder of the three types of SCCC. In Section III, the MAP algorithm applied to SCCC is explained. Some simulation results are shown and analyzed by using the distance spectrum in Section IV. Finally, Section V concludes the paper.

# II. CONCATENATION METHODS OF SCCC

In the encoder of SCCC, the parity bits of outer encoder are necessarily passed to inner encoder through an interleaver and the transfer of the information bits is optional. According to the concatenation method of constituent encoders, there are various structures for SCCC.

In this paper, the model three types of SCCC are presented. The recursive systematic convolutional (RSC) code is used as inner and outer encoder and the overall code rate is 1/3. In order to improve the performance of SCCC, a bit interleaver between component encoders is used. The decoder of the presented SCCC is composed of two MAP modules, interleaver, and deinterleaver.

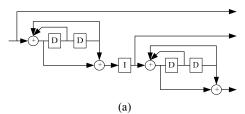

The first type (Type I) of SCCC is shown in Fig. 1, where I and DI denote interleaver and deinterleaver, respectively. And D is 1 bit shift register. As shown in Fig. 1, only the parity bits of the outer encoder are passed to the inner encoder through the interleaver. Therefore the interleaver size is the same as the length of an input frame. The extrinsic values of the information bits of the inner encoder are calculated at MAP1 and then passed to MAP2 through the deinterleaver. And the LLR values of the information bits and the extrinsic values of the parity bits of the outer encoder are calculated at MAP2. The former is used for detection and the latter is fed into MAP1 for iterative decoding.

## World Academy of Science, Engineering and Technology International Journal of Electronics and Communication Engineering Vol:2, No:4, 2008

(a) Encoder (b) Decoder Fig. 1 Structure of Type I

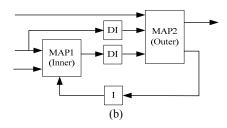

The second type (Type II) of SCCC is shown in Fig. 2, where MUX and DEMUX is each multiplexer and demultiplexer.

(a) Encoder (b) Decoder Fig. 2 Structure of Type II

As depicted in Fig. 2, both the information bits and the parity bits of the outer encoder are transferred to the inner encoder. Therefore, the multiplexer is necessary between the outer encoder and the interleaver and the interleaver size is two times the length of an input frame. In order to set the overall code rate to 1/3, some bits are eliminated by puncturing matrix P, at the last output stage of the encoder. The matrix P is defined by

$$P = \left(\begin{array}{ccc} 1 & 1 & 1 & 1 \\ 1 & 0 & 0 & 1 \end{array}\right).$$

The decoder of Type II is similar to that of Type I. However, the multiplexer and the demultiplexer are required at the decoder. And the extrinsic values of the information bits as well as the parity bits of the outer encoder are also fed into MAP1.

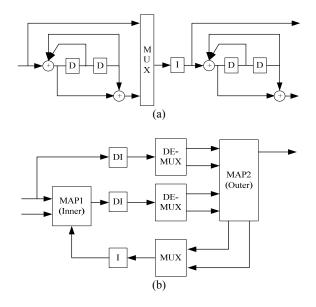

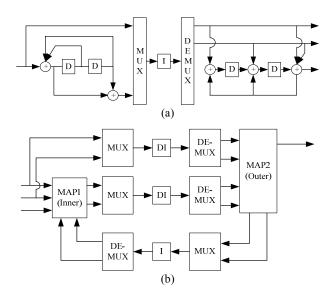

The third type (Type III) of SCCC is shown in Fig. 3. As shown in Fig. 3, the structure of Type III is similar to that of Type II.

(a) Encoder (b) Decoder Fig. 3 Structure of Type III

However, the 2/3-RSC code is used as inner encoder and the demultiplexer is used between the interleaver and the inner encoder in order to set the overall code rate to 1/3. The interleaver size is two times the length of an input frame like Type II. The decoder of Type III is similar to that of Type II excepting that the additional multiplexer and demultiplexer are required.

# III. MAP ALGORITHM TO SCCC

In this paper, the MAP algorithm is used in the iterative decoder of SCCC. It is almost same with the MAP applied to PCCC. However, the LLR values of parity bits as well as information bits might be calculated in the outer decoder (MAP2) of SCCC.

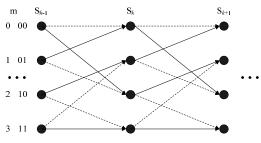

For example, the trellis diagram of the 4-state RSC code with generator [7, 5] is depicted in Fig. 4, where m represents the state number and  $S_k$  is the state at time k. The dotted line represents the state transition when the input bit is 0, and the solid line represents the state transition when the input bit is 1.

At time k, the LLR for the information bit  $u_k$ , is defined as

$$\Lambda(u_k) = \log \frac{P(u_k = 1 | \mathbf{r}_1^L)}{P(u_k = 0 | \mathbf{r}_1^L)},$$

(1)

Fig. 4 Trellis diagram of the RSC code

where  $\mathbf{r}_{l}^{L}$  represents the set from the received symbol  $\mathbf{r}_{1}$  to  $\mathbf{r}_{L}$ . Using the forward and backward parameters [4], [5], (1) can be rewritten as follows:

$$\Lambda(u_k) = \log \frac{\sum_{m} \alpha_k^1(m) \cdot \beta_k(m)}{\sum_{m} \alpha_k^0(m) \cdot \beta_k(m)},$$

(2)

where

$$\alpha_k^i(m) = P(u_k = i, S_k = m, \mathbf{r}_1^k),$$

$$\beta_k(m) = P(\mathbf{r}_{k+1}^L \mid S_k = m).$$

(3)

The forward and backward recursion are performed by

$$\alpha_{k}^{i}(m) = \sum_{n} \sum_{l=0}^{1} \gamma_{i}(\mathbf{r}_{k}, n, m) \cdot \alpha_{k-1}^{l}(n),$$

$$\beta_{k}(m) = \sum_{n} \sum_{l=0}^{1} \gamma_{l}(\mathbf{r}_{k+1}, n, m) \cdot \beta_{k+1}(n).$$

(4)

For example, if the information bit is equal to 0 at time k, then  $\alpha_k^0(m)$  is computed as

$$\alpha_{k}^{0}(0) = \sum_{l=0}^{1} \gamma_{0}(\mathbf{r}_{k}, \mathbf{0}, 0) \cdot \alpha_{k-1}^{l}(\mathbf{0}),$$

$$\alpha_{k}^{0}(1) = \sum_{l=0}^{1} \gamma_{0}(\mathbf{r}_{k}, \mathbf{3}, 1) \cdot \alpha_{k-1}^{l}(\mathbf{3}),$$

$$\alpha_{k}^{0}(2) = \sum_{l=0}^{1} \gamma_{0}(\mathbf{r}_{k}, \mathbf{1}, 2) \cdot \alpha_{k-1}^{l}(\mathbf{1}),$$

$$\alpha_{k}^{0}(3) = \sum_{l=0}^{1} \gamma_{0}(\mathbf{r}_{k}, \mathbf{2}, 3) \cdot \alpha_{k-1}^{l}(\mathbf{2}).$$

(5)

At time k, the LLR for the parity bit  $p_k$ , can be obtained by substituting  $p_k$  for  $u_k$  in (1), (2), and (3). The forward and backward recursion are performed the same as in (4). However, the previous state number contributing to the forward parameter  $\alpha_k^i(m)$  and the post-state number contributing to the backward parameter  $\beta_k(m)$  for the parity bits is each different to those for the information bits. For example, if the parity bit is equal to 0 at time k, then  $\alpha_k^0(m)$  can be calculated as

$$\alpha_{k}^{0}(0) = \sum_{l=0}^{1} \gamma_{0}(\mathbf{r}_{k}, \mathbf{0}, 0) \cdot \alpha_{k-1}^{l}(\mathbf{0}),$$

$$\alpha_{k}^{0}(1) = \sum_{l=0}^{1} \gamma_{0}(\mathbf{r}_{k}, \mathbf{2}, 1) \cdot \alpha_{k-1}^{l}(\mathbf{2}),$$

$$\alpha_{k}^{0}(2) = \sum_{l=0}^{1} \gamma_{0}(\mathbf{r}_{k}, \mathbf{1}, 2) \cdot \alpha_{k-1}^{l}(\mathbf{1}),$$

$$\alpha_{k}^{0}(3) = \sum_{l=0}^{1} \gamma_{0}(\mathbf{r}_{k}, \mathbf{3}, 3) \cdot \alpha_{k-1}^{l}(\mathbf{3}).$$

(6)

#### IV. SIMULATION RESULTS

To evaluate the BER performance of the three types of SCCC in AWGN channel, some simulations have been performed. In these simulations, the overall code rate is 1/3 and the interleaver size is 1000 bits.

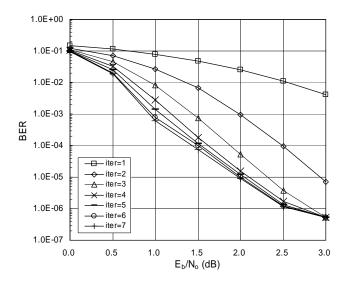

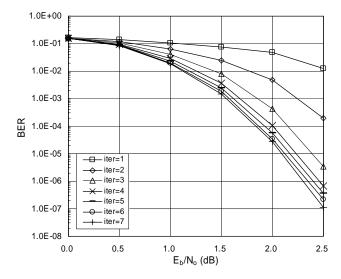

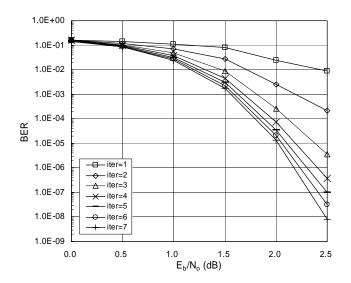

The performance of Type I is shown in Fig. 5. The BER performance of Type I is not improved above the ratio of bit energy to noise power spectral density,  $E_b/N_o$ , of 2.5dB over the five iterations. The performance of Type II and Type III are described in Fig. 6 and 7. As shown in Fig. 6 and 7, the BER performance of Type II is still improved over the five iterations at high  $E_b/N_o$ . The performance of Type III is similar to that of Type II. And Type III shows the better performance at high  $E_b/N_o$  than Type II.

Fig. 5 BER of Type I

Fig. 6 BER of Type II

Fig. 7 BER of Type III

TABLE I PERFORMANCE COMPARISON OF THE THREE TYPES (R=1/3, N=1000, ITER=7)

| BER       | Type I (dB) | Type II (dB) | Type III (dB) |

|-----------|-------------|--------------|---------------|

| 10-3      | 0.90        | 1.55         | 1.60          |

| $10^{-4}$ | 1.40        | 1.80         | 1.80          |

| 10-5      | 2.00        | 2.10         | 2.05          |

| 10-6      | 2.55        | 2.30         | 2.20          |

When the number of iterations is 7, the required  $E_b/N_o$  to obtain the specific BER is shown in Table I. At BER =  $10^{-3}$ , Type I has the coding gain of each 0.65dB and 0.70dB compared to Type II and Type III. The coding gain decreases to 0.10dB and 0.05dB at BER =  $10^{-5}$ . Finally, the performance reversed; Type III has the coding gain of each 0.35dB and 0.10dB compared to Type I and Type II at BER =  $10^{-6}$ .

The simulation results are analyzed using the distance spectrum which is used to calculate the specific upper bound on BER. The general upper bound on BER of concatenated codes in AWGN channel is [2], [8]

$$P_b \le \sum_{d=d_{free}}^{\frac{N}{R}} \left( \sum_{w=1}^{N} \frac{w}{N} A_{w,d} \right) Q\left( \sqrt{d \frac{2RE_b}{N_0}} \right), \tag{7}$$

where N represents the interleaver size, R is the overall code rate, and  $d_{free}$  is the free distance of output codes. And  $A_{w,d}$  is the number of output codes with hamming weight d generated by input codes with hamming weight w. And

$$Q(x) \cong \left[ \left( 1 - \frac{1}{\pi} \right) x + \frac{1}{\pi} \sqrt{x^2 + 2\pi} \right]^{-1} \frac{1}{\sqrt{2\pi}} e^{-\frac{x^2}{2}}.$$

(8)

The distance spectra of the three types with N = 500 are

shown in Table II, where  $W_d$  is equal to  $\sum_{w=1}^{N} w A_{w,d}$  in (7).

TABLE II

DISTANCE SPECTRA OF THE THREE TYPES (R=1/3, N=500, ITER=7)

| Type I |       | Type II |       | Type III |       |

|--------|-------|---------|-------|----------|-------|

| d      | $W_d$ | d       | $W_d$ | d        | $W_d$ |

| 9      | 9     | 18      | 3     | 19       | 3     |

| 10     | 4     | 22      | 5     | 23       | 3     |

| 12     | 8     | 26      | 5     | 24       | 3     |

| 13     | 9     | 28      | 5     | 26       | 5     |

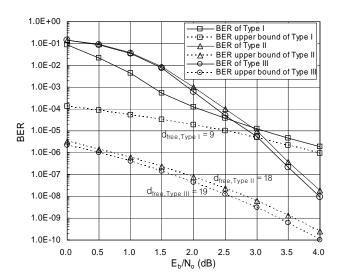

Fig. 8 BER and BER upper bound of the three types

Note that each  $d_{free}$  of the three types is 9, 18, and 19. The upper bound on BER of the three types is obtained by substituting the values of Table II in (7) and (8). Fig. 8 shows the upper bound on BER and the practical BER performance of the three types with R = 1/3, N = 500, and the number of iterations = 7. Since  $d_{free}$  has the greatest influence on the upper bound, the only  $d_{free}$  term in (7) is depicted in Fig. 8. It is shown that the BER performance is closer to the upper bound as  $E_b/N_o$  increases. Especially, the performance of Type I relatively approaches to the upper bound in the low  $E_b/N_o$  range. Therefore, in the  $E_b/N_o$  range from 0 to 2.5 dB, Type I has the best BER performance. On the other hand, above 3.0 dB, the performance is good in order of Type III, II, and I. The order is equal to that of large  $d_{free}$ .

# V. CONCLUSION

In this paper, the BER performance of the three types of SCCC was compared and analyzed in AWGN channel. The simulation results show that the performance of Type I cannot be improved in spite of the increase in the number of iterations at high  $E_b/N_o$ . However, the performance of Type II and Type III are still improved over the five iterations at high  $E_b/N_o$  in the example. And the performance of Type III is better than Type II

#### World Academy of Science, Engineering and Technology International Journal of Electronics and Communication Engineering Vol:2, No:4, 2008

at high  $E_b/N_o$ . In sum, Type I shows the best error correction performance at low  $E_b/N_o$  and Type III shows the best performance at high  $E_b/N_o$ . The distance spectrum was used to analyze the BER performance because the spectrum is strongly related to the BER upper bound. Especially,  $d_{free}$  has the greatest influence on the upper bound. In the example,  $d_{free,TypeIII} = 19$ ,  $d_{free,TypeII} = 18$ , and  $d_{free,TypeII} = 9$ , so the performance is good in the order at high  $E_b/N_o$ .

### REFERENCES

- C. Berrou and A. Glavieux, "Near optimum error correcting coding and decoding: Turbo-codes," *IEEE Trans. Commun.*, vol. 44, no. 10, pp. 261-1271, Oct. 1996.

- [2] S. Benedetto and G. Montorsi, "Unveiling turbo codes: Some results on parallel concatenated coding schemes," *IEEE Trans. Inform. Theory*, vol. 42, no. 2, pp. 409-428, Mar. 1996.

- 3] S. Benedetto and G. Montorsi, "Serial concatenation of block and convolutional codes," *Electron. Lett.*, vol. 32, pp. 887-888, May 1996.

4] L. Bahl, J. Cocke, F. Jelinek, and J. Raviv, "Optimal decoding of linear

- L. Bahl, J. Cocke, F. Jelinek, and J. Raviv, "Optimal decoding of linear codes for minimizing symbol error rate," *IEEE Trans. Inform. Theory*, pp. 284-287, Mar. 1974.

- [5] S. Benedetto, G. Montorsi, D. Divsalar, and F. Pollara, "A softinput soft-output maximum a posteriori (MAP) module to decode parallel and serial concatenated codes," JPL TDA Progress Repert, vol. 42, pp1-20, Nov. 1996

- [6] S. Benedetto, G. Montorsi, D. Divsalar, and F. Pollara, "Serial concatenation of interleaved codes: Performance analysis, design, and iterative decoding," *JPL TDA Progress Report*, vol. 42, pp. 1-26, Aug. 1996.

- A. Ambroze, G. Wade, and M. Tomlinson, "Iterative MAP decoding for serial concatenated convolutional codes," *Proc. IEE Commun.*, vol. 145, no. 2, pp. 53-59, Apr. 1998.

- [8] P. Robertson, "Illuminating the structure of parallel concatenated recursive systematic (turbo) codes," *Proc. IEEE Globecom'94*, San Fransisco, California, pp. 1298-1303, Nov. 1994.

**Dongwon Lee** was born in Daegu, Korea, on October 21, 1976. He received the B.S. and M.S. degrees in electrical engineering from Kyungpook National University, Daegu, Korea in 1999 and 2001, respectively.

From 2001 to 2003, he worked with Agency for Defense Development (ADD), Daejeon, Korea, in the research and development section, developing communication systems for military surveillance. Since 2003, he has been with Samsung Electronics, Youngin-si, Gyeonggi-do, Korea, where he has worked in cellular phone modem development.

His research interests include the hardware architectures and implementation of modulators, channel decoders and digital filters for GSM, EDGE, and WCDMA systems.

**Eon Kyeong Joo** received the B.S. degree in Electronics Engineering from Seoul National University, Seoul, Korea, in 1976, the M.S. and Ph.D. degrees in Electrical Engineering from Ohio State University, Columbus, Ohio, in 1984 and 1987, respectively.

From 1976 to 1979, he was an Officer of Communication and Electronics at Republic of Korea Navy. From 1979 to 1982, he worked for Korea Institute of Science and Technology (KIST) as a Researcher. In 1981, he was awarded the Korean Government Scholarship for graduate study in the USA. In 1987, he joined the faculty of the School of Electronic and Electrical Engineering at Kyungpook National University, Daegu, Korea, where he is now a Professor.

His research interests include digital communication systems, coding and decoding, modulation and demodulation, statistical signal processing, and signal processing for communication systems.