# Discrete-time Phase and Delay Locked Loops Analyses in Tracking Mode

### Jiri Sebesta

Abstract- Phase locked loops (PLL) and delay locked loops (DLL) play an important role in establishing coherent references (phase of carrier and symbol timing) in digital communication systems. Fully digital receiver including digital carrier synchronizer and symbol timing synchronizer fulfils the conditions for universal multi-mode communication receiver with option of symbol rate setting over several digit places and long-term stability of requirement parameters. Afterwards it is necessary to realize PLL and DLL in synchronizer in digital form and to approach to these subsystems as a discrete representation of analog template. Analysis of discrete phase locked loop (DPLL) or discrete delay locked loop (DDLL) and technique to determine their characteristics based on analog (continuous-time) template is performed in this posed paper. There are derived transmission response and error function for 1st order discrete locked loop and resulting equations and graphical representations for 2<sup>nd</sup> order one. It is shown that the spectrum translation due to sampling takes effect at frequency characteristics computing for specific values of loop parameters.

*Keywords*—Carrier synchronization, Coherent demodulation, Software defined receiver, Symbol timing.

#### I. INTRODUCTION

**P**HASE and delay locked loops are the most frequently applied structures in various regulation systems, where the tracked quantity is phase of a signal (or more precisely immediate carrier frequency in communication system) or delay between two signals. Basic motivation for the study of PLL/DLL behavior in discrete domain has been the modernization of universal receiving system for ground station at Department of Radio Electronics. Main requirement of this is to reach high detection efficiency for data signals from experimental satellites with a wide range of bit rates. Therefore the demodulation algorithms have been processed

Manuscript received September 30, 2007. This work has been supported by the post-doctoral grant of Czech Science Foundation No. 102/07/P514 "Research of Digital Detection Methods for Low Energy Signals", by the research grant of Czech Science Foundation No. 102/06/1672 "Communication Systems of Experimental Satellites", and by the research program of Ministry of Education of Czech Republic No. MSM0021630513 "Advanced Electronic Communication Systems and Technologies" (ELCOM).

J. Sebesta was with Brno University of Technology, Czech Republic. He is now with the Department of Radio Electronics, Faculty of Electrical Engineering and Communication, Brno University of Technology, Purkynova 118, 61200 Brno, Czech Republic (e-mail: sebestaj@feec.vutbr.cz). in the digital part of software defined receiver (SDR). This receiver is determined for demodulation of phase shift keying and continuous phase modulations with symbol rates from tens of bauds up to hundreds of kilobauds. Pivotal subsystems of the coherent demodulator are PLL for carrier synchronization and DLL for symbol timing synchronization.

Generally, the PLL or DLL are non-linear systems demanding high-level mathematical computation of highorder non-linear differential equations for determination theirs characteristics, e.g. using Planck-Fokker techniques [1]. Such solution can be simplified by linearization of error detector in tracking mode, where the loop is locked and error value of tracked quantity goes near around equilibrium point. Derivations of analog locked loop characteristics were described in many publications [2], [3], as well as loops in discrete domain based on equivalences with analog forms. Nevertheless, the spectrum translation due to sampling takes effect at resulting frequency characteristics, but in the most of these publications were directly used procedures from analog domain for discrete forms [4]. This phenomenon is the more remarkable the faster response of closed loop is. In following chapters the analyses with sampling implications on resulting frequency characteristics of DPLL/DDLL are executed. The phase or delay loops with fast response bring to bear in the coherent detection of narrow-band satellite signal involved by strong Doppler's effect [5].

### II. DISCRETE PLL AND DLL LINEARIZED MODEL

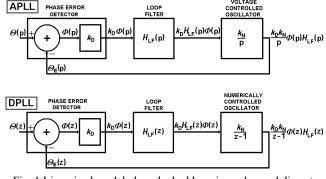

Considering general PLL, results for DLL can be obtained by direct substitution of delay for phase. Block diagram of a linearized PLL in analog domain (APLL) and discrete domain (DPLL) is shown in figure 1. Parameter  $k_D$  is the gain of phase error detector in linearized model and it is specified as a ratio between output error value and true error value of input phase. This parameter corresponds to a slope (derivative) of error detector S-curve in equilibrium point. Function  $H_{\rm LF}(p)$  is a transmission function of loop filter and  $k_{\rm N}$ is gain of voltage controlled oscillator (VCO). Closed-loop transfer function is defined for phase estimation  $\theta_{\rm E}(t)$  and input phase  $\theta(t)$  as a quotient of their transform  $\Theta_{\rm E}(p)$  and  $\Theta(p)$ . Closed loop transfer function in *p*-plane for APLL is given by

$$H_{cA}(p) = \frac{\Theta_E(p)}{\Theta(p)} = \frac{k_D k_N H_{LF}(p)}{p + k_D k_N H_{LF}(p)}$$

(1)

Closed loop transfer function in *z*-plane for DPLL can be analogically got by

$$H_{cD}(z) = \frac{\Theta_E(z)}{\Theta(z)} = \frac{k_D k_N H_{LF}(z)}{z - 1 + k_D k_N H_{LF}(z)}.$$

(2)

Another important function describing features of phase locked loops is error function, which defines transmission between error of phase estimation  $\Phi(p)$  and input phase  $\Theta(p)$ . Putting substitution  $\Theta_{\rm E}(p) = \Theta(p) - \Phi(p)$  together with

Fig. 1 Linearized model phase locked loop in analog and discrete form

equation (1), the error function in p-plane is

$$H_{eA}(p) = \frac{\Phi(p)}{\Theta(p)} = \frac{p}{p + k_D k_N H_{LF}(p)} = 1 - H_{cA}(p).$$

(3)

The error function in z-plane for discrete form of phase locked loop is

$$H_{eD}(z) = \frac{\Phi(z)}{\Theta(z)} = \frac{z-1}{z-1+k_D k_N H_{LF}(z)} = 1 - H_{cD}(z)$$

(4)

By appropriate choice of the loop filter and its transfer function, any order close loop transfer function and error function can be obtained. In this article only the 1<sup>st</sup> and 2<sup>nd</sup> order loops will be taken into consideration. The next chapter derives basic DPLL functions for the simplest configuration of discrete locked loop with 0<sup>th</sup> order loop filter. The following section is focused on discussion of results for discrete 2<sup>nd</sup> order loop.

# III. Derivation of $1^{\rm st}$ order dPll characteristics based on analog template

The 1<sup>st</sup> locked loop contains the 0<sup>th</sup> order loop filter, it means that the multiplying coefficient  $k_0$  (frequency-independent gain) represents loop filter only. The closed-loop transfer function for continuous implementation is given by equation

$$H_{cAlord}(p) = \frac{k_D k_N k_0}{p + k_D k_N k_0} = \frac{K_0}{p + K_0},$$

(5)

where  $K_0 = k_D \cdot k_N \cdot k_0$ . Transfer function defined by formula (5) corresponds to low-pass filter with cut-off frequency  $\omega_m = K_0$ . Asymptotic slope down of transfer modulus in stop-band is 20 dB/dek. Closed loop transfer function for discrete implementation of 1<sup>st</sup> order PLL is

$$H_{cD1ord}(z) = \frac{k_D k_N k_0}{z - 1 + k_D k_N k_0} = \frac{K_0}{z - 1 + K_0}.$$

(6)

The equivalent discrete-time system with continuous-time system, which has low-pass frequency response, can be derived by using impulse-invariance method. This procedure apply the transformation relationship between Laplace transform (p-plane) and Z-transform on poles, it means transform of poles from p-plane to z-plane [3]

$$Z_P = e^{P_P \cdot T_{Sa}} \,. \tag{7}$$

$T_{\rm Sa}$  is sampling period of discrete system and its value has to satisfy sampling theorem

$$H_{cA}(\omega) = 0 \quad for \quad \omega \ge \frac{\omega_{Sa}}{2}, \tag{8}$$

Formulation of single pole of 1<sup>st</sup> order DPLL, which is derived from APLL system by (7), is

$$Z_P = e^{-\omega_m \cdot T_{Sa}} = e^{-2\pi \frac{\omega_m}{\omega_{Sa}}} = e^{-2\pi \cdot \Omega_m} .$$

<sup>(9)</sup>

Fig. 2 Close loop frequency responses of 1st order DPLL

Parameter  $\Omega_m$  is defined as normalized cut-off frequency of  $1^{\text{st}}$  order DPLL

$$\Omega_m = \frac{\omega_m}{\omega_{Sa}} = \frac{f_m}{f_{Sa}} \tag{10}$$

and it is possible to set it in range (0, 0.5).

Coefficient  $K_0$  in (6) is derived by confrontation of the pole in (9) and the denominator of closed loop transfer function (6)

$$K_0 = 1 - e^{-2\pi \cdot \Omega_m}$$

(11)

Finally, the closed-loop transfer function of 1<sup>st</sup> order DPLL is given by substitution (11) in (6)

$$H_{cDlord}(z) = \frac{K_0}{z - 1 + K_0} = \frac{1 - e^{-2\pi \cdot \Omega_m}}{z - e^{-2\pi \cdot \Omega_m}}.$$

(12)

Similarly, the error function of 1<sup>st</sup> order DPLL is determined by formula

$$H_{eDlord}(z) = 1 - \frac{K_0}{z - 1 + K_0} = \frac{z - 1}{z - 1 + K_0} = \frac{z - 1}{z - e^{-2\pi \cdot \Omega_m}}.$$

(13)

The closed loop frequency response of 1<sup>st</sup> order DPLL is presented in figure 2, where the slope down of modulus in stop-band less than 20 dB/dec is obvious and this value decreases with growing  $\Omega_m$ . It is implication of imperfect fulfillment of sampling theorem (8), or effect of aliasing. Because of the aliasing that occurs in the sampling process, the frequency response and behavior of the DPLL is not identical to the original APLL.

The last step of 1<sup>st</sup> order DPLL analyses is the determination of stability conditions. Single pole of DPLL system is given by formula (9), it lies on real axis inside of unity circle for any  $\Omega_m$  in possible range (0, 0.5). Due to the 1<sup>st</sup> order DPLL is unconditionally stable.

## IV. 2<sup>ND</sup> ORDER DPLL CHARACTERISTICS

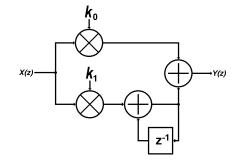

Analogically as the discrete 1<sup>st</sup> order locked loop characteristics computation, the 2<sup>nd</sup> order DPLL characteristics were derived. Block diagram of discrete loop filter for 2<sup>nd</sup> order PLL is shown in figure 3. There are several configurations of such loop filter, so following calculations represent DPLL system with filter in arrangement in figure 3. The derivation of DPLL characteristics was based on the 2<sup>nd</sup> order analog PLL with integrator described by closed loop transfer function []

$$H_{cA2ord}(p) = \frac{2\zeta \omega_n p + \omega_n^2}{p^2 + 2\zeta \omega_n p + \omega_n^2},$$

(14)

where  $\omega_n$  is the natural frequency and  $\zeta$  is the dumping factor. The two poles of transfer (14) are

$$P_{P0} = -\zeta \omega_n + j \omega_n \sqrt{1 - \zeta^2}.$$

$$P_{P1} = -\zeta \omega_n - j \omega_n \sqrt{1 - \zeta^2}.$$

(15)

The poles of discrete PLL form in z-plane are calculated by applying the impulse invariance method (7) mentioned above

$$Z_{P0} = e^{P_{P0}T_{S_{\alpha}}} = e^{T_{S_{\alpha}}\left(-\zeta\omega_{n} + j\omega_{n}\sqrt{1-\zeta^{2}}\right)}.$$

$$Z_{P1} = e^{P_{P1}T_{S_{\alpha}}} = e^{T_{S_{\alpha}}\left(-\zeta\omega_{n} - j\omega_{n}\sqrt{1-\zeta^{2}}\right)}.$$

(16)

$T_{\text{Sa}}$  represents sampling period of discrete PLL system. The same procedure as in case of 1<sup>st</sup> DPLL was used and resulting formula of closed loop transfer for 2<sup>nd</sup> order DPLL was computed

$$H_{cD2ord}(z) = \frac{z \cdot 2\left|1 - e^{-2\pi\zeta\Omega_n} \cdot \cos\left(2\pi\Omega_n\sqrt{1-\zeta^2}\right)\right| + e^{-4\pi\zeta\Omega_n} - 1}{z^2 - z \cdot 2e^{-2\pi\zeta\Omega_n} \cdot \cos\left(2\pi\Omega_n\sqrt{1-\zeta^2}\right) + e^{-4\pi\zeta\Omega_n}} \quad for \quad \zeta \le 1.$$

(17)

$$= \frac{z \cdot 2\left[1 - e^{-2\pi\zeta\Omega_n} \cdot \cosh\left(2\pi\Omega_n\sqrt{\zeta^2-1}\right)\right] + e^{-4\pi\zeta\Omega_n}}{z^2 - z \cdot 2e^{-2\pi\zeta\Omega_n} \cdot \cosh\left(2\pi\Omega_n\sqrt{\zeta^2-1}\right) + e^{-4\pi\zeta\Omega_n}} \quad for \quad \zeta > 1$$

The parameter  $\Omega_n$  is defined as the normalized natural frequency relating to sampling frequency. The dumping factor has the same meaning and rate as in case of APLL. The coefficients of loop filter (see figure 3) are derived from transfer function (17)

$$k_{0} = \frac{\frac{2}{k_{D}k_{N}} \left[ 1 - e^{-2\pi\zeta\Omega_{n}} \cos\left(2\pi\Omega_{n}\sqrt{1-\zeta^{2}}\right) \right] \qquad \zeta \leq 1$$

$$k_{0} = \int for$$

$$\frac{2}{k_{D}k_{N}} \left[ 1 - e^{-2\pi\zeta\Omega_{n}} \cosh\left(2\pi\Omega_{n}\sqrt{\zeta^{2}-1}\right) \right] \qquad \zeta > 1$$

(18)

Fig. 3 Block diagram of loop filter for 2<sup>nd</sup> order DPLL

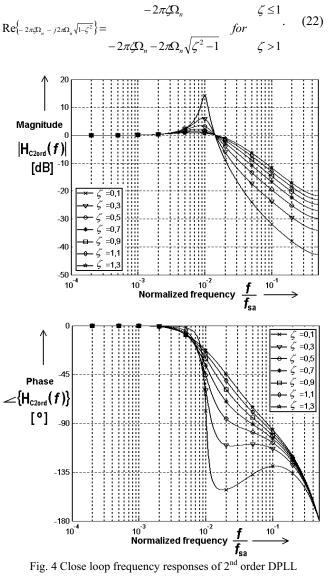

An example of frequency responses of 2<sup>nd</sup> order DPLL is shown in figure 4. There is again evident the impact of aliasing that occurs in the sampling process.

In the end, the stability of proposed discrete-time system was investigated. If the one pole in equation (15) is complex number, the second one is complex conjugate. Then one of them can be investigated and stability of  $2^{nd}$  order DPLL system is given by

$$\left| e^{\left(-2\pi\zeta\Omega_n - j2\pi\Omega_n\sqrt{1-\zeta^2}\right)} \right| \le 1.$$

(20)

This condition can be rewritten on based of exponential function properties as investigation of a real part of exponent

$$\operatorname{Re}\left\{-2\pi\zeta\Omega_{n}-j2\pi\Omega_{n}\sqrt{1-\zeta^{2}}\right\}\leq0.$$

(21)

Analytic solution of the real part of exponent can be divided in two intervals

$(\Omega_n = 0.01)$

Because of the normalized natural frequency  $\Omega_n$  and the dumping factor  $\zeta$  are always positive the condition (21) is fulfilled at all times and this configuration of 2<sup>nd</sup> order DPLL is also unconditionally stable.

### V. CONCLUSION

In the paper an analyses of discrete form of phase locked loops was executed. Crucial aspect of resulting analyses is that the aliasing originating in sampling process affects the characteristics of DPLL or DDLL, especially in fast loops. It is important for a design of narrow band systems, where the fluctuation of tracked quantities could be sizable, as in satellite or deep-space communication.

Because the close loop transfer is corresponding to transfer of low-pass filter with unity gain in pass-band, the error function has to have a character of high-pass filter with the same cut-off frequency as the close loop. The result of this is that the phase drift with low-frequency components do not take effect on phase error. On the contrary, the fast phase drift has more significant impact on phase error.

### REFERENCES

- H. L. Van Trees, Detection, estimation, and modulation theory II. Nonlinear Modulation Theory. John Wiley & Sons, 2003.

- [2] X. Chi, "Carrier Recovery Using a Second Order Costas Loop," DSP Implementation of Communication Systems ECPE 4654 Experiment 5, April 2002.

- [3] P. Chen, J. Henkelman, "Design Considerations for Digital Phase-Locked Tracking Loops Used in a Digital Receiver," *Application sheet* AN-313, Intersil Cororation, 1999.

- [4] A. Mileant, S. Million, S. Hinedi, U. Cheng, "The Performance of the All-Digital Data Transition Tracking Loop Using Nonlinear Analysis," *IEEE Transactions on Communications*, vol. 43, no. 2-4, pp. 1202 – 1214, Feb.-Apr. 1995.

- [5] A. Blanchard, Phase-Locked Loops: Application to Coherent Receiver Design. John Wiley & Sons, 1976.

- [6] G. Skiller, D. Huang, "The Stationary Phase Error Distribution of a Digital Phase-Locked Loop," *IEEE Transactions on Communications*, vol. 48, no. 6, pp. 925 – 927, Jun. 2000.

- [7] O. Yaniv, D. Raphaeli, "Near-Optimal PLL Design for Decision-Feedback Carrier and Timing Recovery," *IEEE Transactions* on Communications, vol. 49, no. 9, pp. 1669 – 1678, Sep. 2001.

- [8] A. Patapoulitan, "On Phase-Locked Loops and Kalman Filters," *IEEE Transactions on Communications*, vol. 47, no. 5, pp. 670 672, May 1999.

**J.** Sebesta (M'05) was born in Brno in 1973. In 1997, he graduated in communication engineering from the Faculty of Electrical Engineering, Brno Univ. of Technology (BUT), Czech Republic (CZE). In 2005, he obtained PhD degree in radio engineering from the Faculty of Electrical Engineering and Communication, BUT, CZE.

He worked as research worker in Academy of Sciences of the Czech Republic at the Department of Nuclear Magnetic Resonance. In present, he is an assistant at the Department of Radio Electronics. He became a Member (M) of IEEE in 2005, and Member of AMSAT in 2005.

Dr. Sebesta is member of IEEE Aerospace and Electronic System Society and candidate of committee of IEEE Czech-Slovak section.