# A Low Power High Frequency CMOS RF Four Quadrant Analog Mixer

M. Aleshams, A. Shahsavandi

**Abstract**—This paper describes a CMOS four-quadrant multiplier intended for use in the front-end receiver by utilizing the square-law characteristic of the MOS transistor in the saturation region. The circuit is based on 0.35 um CMOS technology simulated using HSPICE software. The mixer has a third-order inter the power consumption is 271uW from a single 1.2V power supply. One of the features of the proposed design is using two MOS transistors limitation to reduce the supply voltage, which leads to reduce the power consumption. This technique provides a GHz bandwidth response and low power consumption.

*Keyword*—RF-Mixer, Multiplier, cut-off frequency, power consumption

# I. INTRODUCTION

A swireless products such as cellular phones, global system for mobile communications (GSM), global positioning satellite (GPS), wire-less local area network (WLAN) have become a part of people's life, the need for higher performance at low costs and low power consumption of these products becomes more and more important.

On the other hand, an important block in the receiver of these systems is the mixer. The operation of a mixer can be based on an analog multiplier circuit.

In this paper a new CMOS four-quadrant analog multiplier is proposed. In section 2 the design of our proposed circuit is presented. The simulation results of this multiplier are given and compared to those of some similar circuits designed in [1-3].

# II. THE PROPOSED MULTIPLIER

Usually, the variable trans-conductance technique which operates on Gilbert's trans-linear circuit is widely used to design multiplier circuits in bipolar and CMOS technologies [4-6]. The other approaches in CMOS technology are based on square-law characteristics of MOS transistors biased in the saturation region [7-8] or based on the current voltage characteristics of CMOS transistors biased in the nonsaturation region [9-10].

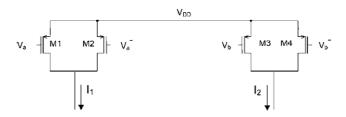

Our proposed multiplier is based on the square-law characteristics of MOS transistors biased in the saturation region. The operation of four PMOS transistors to describe

this law is shown in Fig. 1. Voltage  $V_a$  consists of two components DC and AC whereas voltage  $V_a^-$  has the same DC component but negative AC. This condition is valid for voltages  $V_b$  and  $V_b^-$ . The drain current of each transistor can be expressed as

$$I_{D1} = \frac{K}{2} \left( V_{DD} - V_a - V_T \right)^2 \tag{1}$$

$$I_{D2} = \frac{K}{2} \left( V_{DD} - V_a^{-} - V_T \right)^2$$

(2)

$$I_{D3} = \frac{K}{2} (V_{DD} - V_b - V_T)^2$$

(3)

$$I_{D4} = \frac{K}{2} \left( V_{DD} - V_{b}^{-} - V_{T} \right)^{2}$$

<sup>(4)</sup>

where K can be taken as process technology constant,  $V_{DD}$  is the power supply, and  $V_T$  is the threshold voltage for each transistor. By some definitions as follows

$$V_a = V_1^+ + V_2^-$$

(5)

$$V_b = V_1^- + V_2^+ \tag{6}$$

$$V_1^+ = V_{DC1}^- + V_1^- \tag{7}$$

$$V_1^- = V_{DC1} - V_1 \tag{8}$$

$$V_2^{+} = V_{DC2}^{-} + V_2^{-} \tag{9}$$

$$V_2^{-} = V_{DC2} - V_2 \tag{10}$$

then we have

$$I_{1} = I_{D1} + I_{D2} = \begin{cases} \frac{K}{2} \left\{ 2 \left( V_{DD} - V_{DC2} - V_{DC1} - V_{T} \right)^{2} + 2V_{1}^{2} + 2V_{2}^{2} + 4V_{1}V_{2} \right\} \end{cases}$$

(11)

and

$$I_{2} = I_{D3} + I_{D4} = \begin{cases} \frac{K}{2} \left\{ 2 \left( V_{DD} + V_{DC2} - V_{DC1} - V_{T} \right)^{2} + 2V_{1}^{2} + 2V_{2}^{2} - 4V_{1}V_{2} \right\} \end{cases}$$

(12)

Dpen Science Index, Electrical and Computer Engineering Vol:5, No:12, 2011 publications.waset.org/4910.pdf

M. aleshams Dept. of Electrical Engineering, Fasa Branch, Islamic Azad University, Fasa, Iran, E-mail: m.alshams@iaufasa.ac.ir

A. shahsavandi M.S. Student of Dept. of Electrical Engineering, Fasa Branch, Islamic Azad University, Fasa, Iran, E-mail: A\_shahsavandi@yahoo.com.

Thus one can obtain the following useful equation

$$I_1 - I_2 = 4KV_1V_2 \tag{13}$$

Fig. 1 Four MOS transistors used to describe the square-law characteristics

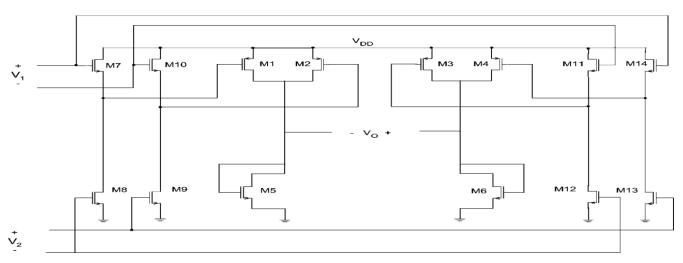

The proposed four-quadrant multiplier is shown in Fig. 2. The design of this multiplier is based on the circuit shown in Fig.1 and consists of 14 MOS transistors operating in the saturation region except for M5 and M6. These two transistors work as two linear resistors whose resistance can be described as [11]

$$R = \frac{1}{K\left(V_{GS} - V_T\right)} \tag{14}$$

Then using (13) the differential output of the multiplier is

$$V_o = 4RKV_1V_2 \tag{15}$$

### III. SIMULATION RESULTS

The performance of the proposed analog multiplier circuit is simulated using HSPICE and parameters based on 0.35  $\mu$ m CMOS technology [12]. The supply voltage  $V_{DD}$  is +1.2 V while the aspect ratios for all transistors are given in Table I.

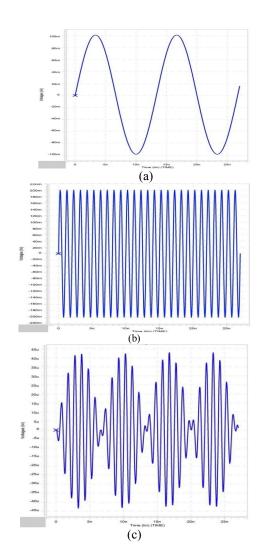

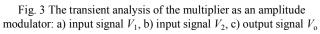

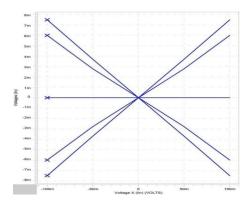

In order to analysis of the multiplier as an amplitude modulator, we set  $V_1$  and  $V_2$  as 300 MHz and 3 GHz sinusoidal input signals with peak amplitude of 100mV, respectively. Fig. 3 shows the transient response of the modulator. Fig. 4 shows the DC transfer characteristics of the proposed analog multiplier without any load while the input voltage range is  $\pm 100$  mV.

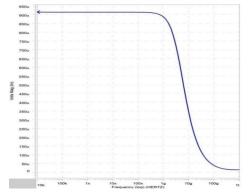

This multiplier has also a GHz-bandwidth response with a cut-off frequency of 4.14 GHz as shown in Fig.5. This high frequency response can be due to small aspect ratios for the circuit's transistors.

The calculated power consumed in the proposed multiplier is 192  $\mu$ W. In fact, using fewer transistors in comparison with some other similar circuits [1] can lead to smaller required supply voltage and hence smaller power consumption. The simulated results for the proposed multiplier are summarized and compared to those for some similar circuits in Table II.

#### REFERENCES

Mohammed K. Salama and Ahmed. M. Soliman "Low-Voltage Low-Power CMOS RF Four-QuadrantMultiplier" Int. J. Electron. Commun. (AE"U) 57 (2003) No. 1, 74–78.

- [2] W. Liu and Sh. Iuan Liu, "Design of a CMOS low-power and low-voltage four-quadrant analog multiplier" springer science +business media, 16 september 2009.

- [3] C. Sakul and K. Pongthana, "a low voltage supply four quadrant analog multiplier circuit" ieee International Symposium on Intelligent Signal Processing and Communication Systems, 2009, pp. 292-294.

- [4] B. Razavi, "Design of Analog Integrated Circuits", New York: McGraw-Hill, 2001, pp. 126–129.

- [5] N I. KHACHAB, A-AZIZ AL-SAQER AND J G. VARGHESE "High Linearity BiCMOS Multiplier/Transconductor Structures" Analog Integrated Circuits and Signal Processing, 16, 1998, pp. 47-61.

- [6] SHEN-IUAN LIU, J-L LEE AND CH-CH CHANG "Low-Voltage BiCMOS Four-Quadrant Multiplier and Squarer" Analog Integrated Circuits and Signal Processing, 20, 1999, pp. 25-29.

- [7] B. Bunchu and W. Surakampontorn "voltage mode CMOS squarer multiplier circuit" king mongkut s institute of technology ladkrabang.

- [8] Witold Machowski, Stanisław Kuta, Jacek Jasielski "Four-quadrant analog multiplier based on CMOS inverters" Analog Integr Circ Sig Process 55, 2008, pp. 249–259.

- [9] R. Hidayat, K. Dejhan, P. Moungnoul, and V. Miyanaga "ota based high frequency CMOS and squaring circuit" King Mongkut's Institute of Technology Ladkrabang, Bangkok 10520, Thailand.

- [10] SIMON CIMIN LI " A Symmetric Complementary Structure for RF CMOS Analog Squarer and Four-Quadrant Analog Multiplier" Analog Integrated Circuits and Signal Processing, 23, 2000, pp. 103-115.

- [11] Moon, G.; Zaghloul, M.E.; Newcomb, R.W.: An Enhancement Mode MOS Voltage-Controlled Linear Resistor with Large Dynamic Range. IEEE J. Circuits and Systems 37 (1990), 1284–1288.

- [12] MOSIS, Wafer Electrical Test Data and SPICE Model Parameters TSMC (0.09µm).

| TABLE I                                       |         |  |  |  |

|-----------------------------------------------|---------|--|--|--|

| ASPECT RATIO, W/L                             |         |  |  |  |

| Transistor Aspect ratio $(^{\mu m}/_{\mu n})$ |         |  |  |  |

| M1-M4                                         | 7/0.35  |  |  |  |

| M5-M6                                         | 10/0.35 |  |  |  |

| M7-M14                                        | 10/0.35 |  |  |  |

|                                               |         |  |  |  |

TABLE II

| TABLE II<br>THE SIMULATED PARAMETERS FOR DIFFERENT ANALOG MULTIPLIERS |                        |         |        |            |  |

|-----------------------------------------------------------------------|------------------------|---------|--------|------------|--|

| Parameter                                                             | Proposed<br>Multiplier | [1]     | [2]    | [3]        |  |

| Supply voltage                                                        | 1.2V                   | 1.5V    | 1.5V   | 2.5V       |  |

| Number of<br>MOS<br>transistors                                       | 14                     | 16      | 8      | 16         |  |

| Power<br>dissipation                                                  | 192µW                  | 1.18 mW | 6.7µW  |            |  |

| Cut-off<br>frequency                                                  | 4.14GHZ                | 900MHz  | 268KHz | 197MH<br>z |  |

| Technology                                                            | 0.35µm                 | 0.5µm   | 0.35µm | 0.5µm      |  |

# World Academy of Science, Engineering and Technology International Journal of Electrical and Computer Engineering Vol:5, No:12, 2011

Fig. 2 The proposed multiplier

Fig. 4 DC transfer characteristics of the multiplier

Fig. 5 The frequency response of the multiplier