# New Gate Stack Double Diffusion MOSFET Design to Improve the Electrical Performances for Power Applications

Z. Dibi, F. Djeffal, and N. Lakhdar

Abstract—In this paper, we have developed an explicit analytical drain current model comprising surface channel potential and threshold voltage in order to explain the advantages of the proposed Gate Stack Double Diffusion (GSDD) MOSFET design over the conventional MOSFET with the same geometric specifications that allow us to use the benefits of the incorporation of the high-k layer between the oxide layer and gate metal aspect on the immunity of the proposed design against the self-heating effects. In order to show the efficiency of our proposed structure, we propose the simulation of the power chopper circuit. The use of the proposed structure to design a power chopper circuit has showed that the (GSDD) MOSFET can improve the working of the circuit in terms of power dissipation and self-heating effect immunity. The results so obtained are in close proximity with the 2D simulated results thus confirming the validity of the proposed model.

*Keywords*—Double-Diffusion, modeling, MOSFET, power.

# I. INTRODUCTION

POWER field-effect transistors (MOSFETs) have been focus of interest both from applications and fundamental research point of views. Today, high-voltage MOS devices are extensively used in all kinds of integrated power circuits, like switch-mode power supplies, choppers, and power amplifiers [1]-[3]. As the MOSFET is biased with high voltages, the advantages of power MOSFET are diminished by the selfheating-effects [1]-[4]. These effects lead to the working limitations on conventional planar MOSFETs. To overcome these limitations and realize high-performance MOS transistors, a new transistor called Double Diffused (DD) MOSFET has been proposed as potential candidate for power CMOS-based circuits' design [3,4]. But, the continued scaling of SiO2-based gate dielectrics leads to a large gate leakage and therefore, DD MOSFET performances can be degraded [3]-[5]. To minimize self-heating-effects and improve drain current, a new design and improvement of conventional DD MOSFETs become indispensable. In this work, a new design of DD MOSFET called gate stack (GS) double-diffused (DD)

MOSFET, in which the gate leakage and self-heating-effects will be greatly improved, is proposed for the future power electronics circuits. In the proposed design, the average electric field under the gate further increases and the high density of interface hot-carrier at the drain end region can be reduced using the gate stack design.

The aim of this paper is to present an analytical model comprising channel potential and drain current in order to explain the advantages of the proposed (GSDD) MOSFET over the conventional DDMOSFET with the same geometrics specifications that allow us to utilize the benefits of the incorporation the high-k layer aspect on the immunity of the proposed design against the self-heating-effects. The results so obtained are in close proximity with the simulated results thus confirming the validity of the proposed model.

This paper is organized as follows. In section.2, we develop a compact analytical model for drain current based on surface potential aspect in order to analyse the device immunity against the self-heating-effect. In Section 3, we investigate the immunity of the DD MOSFETs with additional high-k layer (Gate Stack) against the self-heating-effect degradation. Moreover, the implementation of the proposed design into circuits' simulator allows us to analyse the impact of the proposed approach on the performances of the power electronic circuits. The conclusions will be drawn in Section 4.

## II. MODELING METHODOLOGY

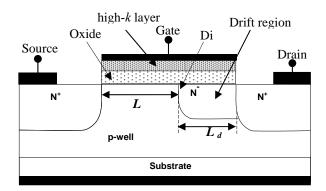

In Fig.1 a cross section of a high-voltage GSDD MOSFET is given. The-well bulk is diffused from the source-side under the gate (G), and thus forms a graded channel region. The internal-drain Di represents the point where the graded channel turns into the lightly doped region. With the gate extending over the drift region, an accumulation layer forms in the drift region underneath the gate oxide. Therefore, above the threshold voltage of the channel region, electrons flow through an inversion channel from the source toward the drain terminal at the end of the drift region. The structure has a double-layer gate stack, oxide and high-k layers, the effective oxide layer thickness of insulator layer toxeff is given by the superposition of the thickness of the  $SiO_2$  layer t1 with permittivity  $\mathcal{E}_1$  and the thickness of the high-k layer t2 having permittivity  $\mathcal{E}_2$  as follows,

F. Djeffal and Z. Dibi are with the Department of Electronics, University of Batna, Batna 05000, Algeria (phone: 00213773796503; fax: 0021333805494; e-mail: faycaldzdz@hotmail.com).

N. Lakhdar is with the Department of Electronics, University of Batna, Batna 05000, Algeria (phone: +213-664314357; e-mail: nacereddine\_1@hotmail.fr).

$$t_{oxeff} = t_1 + (\varepsilon_1 / \varepsilon_2)t_2 \tag{1}$$

$$\mu_{ch} = \frac{\mu_{eff}}{1 - \epsilon_2}$$

Fig. 1 Cross section of the GSDD MOSFET investigated in this work.

In the analytical modeling approach, expressions for the current through the inversion channel,  $I_{ch}$ , as well as for the current through the drift region,  $I_{dr}$ , should be derived in order to develop our drain current model as function of the internal-drain Di. This internal-drain voltage is expressed explicitly in terms of the external terminal voltages. The expression for this internal drain voltage is derived by equating  $I_{ch}$  to  $I_{dr}$ . Next, the internal drain voltage is used to calculate the surface potentials, in which the final drain current is formulated. In this way,  $I_{ds}$  is surface-potential based and it is explicitly expressed in terms of the external terminal voltages and fitting parameters which will be calculated using genetic algorithm approach.

The channel current for DD MOSFET is expressed as [6]-[8],

$$I_{ch} = \frac{W\mu_{ch}C_G}{L_{ch}} (V_{inv0} - 0.5\zeta\Delta\psi_s + \zeta V_{th})\Delta\psi_s \tag{2}$$

where, W is the gate width,  $\mu_{ch}$  represents the electron mobility in the channel,  $C_G = \varepsilon_1 / t_{oxeff}$  is the gate capacitance per unit area,  $V_{inv0}$  represents the inversion voltage per unite area at the source side. The parameter  $\zeta$  reflects the variation of inversion charge in the channel region with surface potential.  $\Delta \psi_s = \Psi_{sL} - \Psi_{s0}$  is the surface potential drop across the channel region (difference between the surface potential at internal-drain point and source-side one), and  $V_{th}$  represents the thermal voltage.

Velocity saturation in the channel is calculated for by taking the mobility  $\mu_{\it eff}^{\it ch}$  equal to

$$\mu_{ch} = \frac{\mu_{eff}}{1 + \alpha_3 \Delta \psi_s} \tag{3}$$

where  $\mu_{\it eff}$  is the effective electron mobility in the channel,  $\alpha_3(\alpha_1,\alpha_2)=\mu_0^{\it ch}(\alpha_1,\alpha_2)/(L_{\it ch}v_{\it sat}(\alpha_1,\alpha_2))$  represents the model parameter which describes the velocity saturation in channel region, with  $\mu_0^{\it ch}$  the low field electron mobility in the channel and  $v_{\it sat}$  represents the saturation electron mobility. It is to note that the model parameters  $\alpha_3,\alpha_1$  and  $\alpha_2$  are calculated using genetic algorithm technique, in which the fitness function is defined as,

$$f = \frac{1}{M} \sum_{V_{ds}} \sum_{V_{as}} \left[ \frac{I_{ds,NUM} - I_{ds,ANA}}{I_{ds,NUM}} \right]^{2}$$

(4)

where f is the fitness value;  $I_{ds,ANA}$  is the predicted drain current based on analytical computation;  $I_{ds,NUM}$  represents the target function (numerical results based on 2-D numerical simulation [9]); and M represents the number of samples (database size). It is aimed to minimize this fitness function in order to improve the accuracy of the analytical drain current model for GSDD MOSFETs.

In the linear working regime, the drift current  $I_{dr}$  is expressed as,

$$I_{dr} = \frac{W\mu_{acc}}{L_d} \int_{V_{Di}}^{V_D} (-Q_{acc}^{dr}) dV_C + \frac{W\mu_{dr}}{L_d} \int_{V_{Di}}^{V_D} (-Q_b^{dr}) dV_C$$

(5)

where the first term of (5) represents the current through the accumulation layer, and the second one the current through the bulk.  $\mu_{acc}$  is the electron mobility through the accumulation layer, while  $\mu_{dr}$  is that through the bulk. In addition,  $Q_{acc}^{dr}$  and  $Q_{b}^{dr}$  represent the charge per unit area in the accumulation and bulk regions, respectively.  $V_{C}$  is the channel voltage in drift region.

An approximate computation of (5) is given by as,

$$I_{dr}(\theta_{1}, \theta_{2}, \theta_{3}) = \frac{f_{lin}(\theta_{1}, \theta_{2}, \theta_{3})}{R_{D}} V_{DDi}$$

$$+ \frac{W \mu_{acc}(\theta_{1}, \theta_{2}, \theta_{3}) C_{G}}{2L_{d}} ((V_{accDi})^{2} - (V_{accD})^{2})$$

(6)

where  $V_{accDi}$  and  $V_{accD}$  represent the voltage value at internal drain point and drain side, respectively.  $R_D$  is the onresistance in drift region, the parameters  $\theta_i$  are the fitting parameters can be extracted using genetic algorithm technique (4).

In order to derive an explicit analytical model of drain current, the expressions for drain current in the channel and drift regions are obtained separately. These expressions are then equated and simplified to obtain a second order polynomial for the channel current in terms of the unknown internal drain potential  $V_{Di}$  (under the imposed constraint  $(0 \le V_{Di} \le V_{ds})$ ), and the solution of this latter equation for  $V_{Di}$  is explicitly expressed in terms of the external applied voltages.

### III. RESULTS AND DISCUSSIONS

In this section, the accuracy and various properties of the DD and GSDD MOSFETs current model will be studied and analyzed by comparing the obtained results with 2D numerical simulations in order to show the effect of the induced high-*k* layer on the improvement of the device performances in terms of drain current values and self-heating-effects immunity.

The obtained analytical and numerical *I-V* characteristics of DD and GSDD MOSFETs with are given in Fig.2. It can be seen that GSDD design has higher current as compared to DD device and the analytical results are found to be in close agreement with the simulated results. This increasing in drain current can be explained by the effect of the introduced high-*k* layer on the limitation of oxide tunnel current and the improvement of the gate-channel controllability. Moreover, the self-heating-effect degradation becomes more apparent when the applied gate voltage is increased to higher values. In this case, it clear shown that a great immunity against this degradation has been observed for GSDD design. Therefore, the GSDD MOSFET brings prominent advantages in terms of immunity against the self-heating-effect degradation and delivered drain current compared to DD MOSFETs.

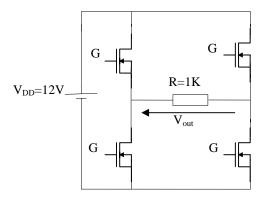

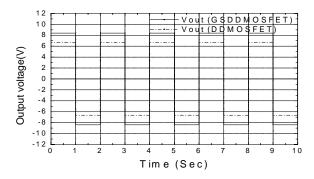

In order to show the impact of our proposed design, we propose the simulation of the power chopper CMOS circuit, which is considered as an important device for power electronics applications. However, as the CMOS technology enters the high power regime, nonlinear effects and selfheating-effect degradation become more and more important and consequently an improvement of thermal behavior of a DD MOSFET is necessary. In this study, using the developed analytical models, we have simulated a power chopper CMOS circuit. The purpose of this simulation is to study the evolution of the output voltage as function of transistor design. The power chopper CMOS circuit consists of four GSDD MOSFETs (Fig. 3). The output voltages characteristics of the power chopper were predicted using the implemented analytical models into simulator library as it is shown in Fig. 4. It is clear that an improvement of the output voltage has been recorded in the case of GSDD MOSFET-based chopper.

Fig. 2  $I_{ds}$ - $V_{ds}$  characteristics of the DD MOSFET including self-heating- effects for both designs: with and without high-k layer ( $t_1$ =15nm, L=0.8 $\mu$ m, L<sub>d</sub>=0.8 $\mu$ m,  $t_2$ =15nm and W=17  $\mu$ m).

This improvement can be explained by the high electrical performances (high drain current, low ON-resistance, self-heating immunity,...) of our proposed design.

Fig.3 Circuit diagram of the GSDD MOSFET-based chopper.

Fig. 4 Pspice output signals for both designs: DD MOSFET and GSDD MOSFET-based choppers.

# IV. CONCLUSION

In this paper, a new design of DD MOSFET by introducing of high-k layer is presented. The performances of the proposed design were compared to the conventional DD MOSFET, illustrating the superior performance of the proposed design with respect to the conventional DD MOSFET in terms of thermal behavior and electrical performances. The encouraging obtained results have indicated that the proposed design is particularly suitable to be incorporated into electronic devices simulators to study and improve the CMOS-based circuits for power electronics applications.

### REFERENCES

- R.S. Scott, G.A. Franz, and J.L. Johnson," An accurate model for power DMOSFETs including interelectrode capacitances," *IEEE Tran. Power Electron*, vol. 6, pp. 192-198, 1991.

- [2] Y. Kim, J.G. Fossum, and R.K. Williams," New Physical Insights and Models for High-Voltage LDMOST IC CAD," *IEEE Tran. Electron Devices*, vol. 7, pp. 1641-1649, 1991.

- [3] R. Sithanandam and M. J. Kumar," Linearity and speed optimization in SOI LDMOS using gate engineering," *Semicond. Sci. Technol*, vol. 25, 6pp. 015006, 2010.

- [4] J.G. Fiorenza, and J. A. del Alamo," Experimental Comparison of RF Power LDMOSFETs on Thin-Film SOI and Bulk Silicon," *IEEE Trans. Electron Devices*, vol. 49, pp. 687-692, 2002.

- [5] R.S. Saxena and M.J. Kumar," Dual-Material-Gate Technique for Enhanced Transconductance and Breakdown Voltage of Trench Power MOSFETs," *IEEE Trans. Electron Devices*, vol. 56, pp. 517-522, 2009.

- [6] A.C.T. Aarts, N. D'Halleweyen, and R. van Langevelde," A Surface-Potential-Based High-Voltage Compact LDMOS Transistor Model," *IEEE Trans. Electron Devices*, vol. 52, pp. 999-1007, 2005.

- [7] A.C.T. Aarts, W.J. Kloosterman," Compact Modeling of High-Voltage LDMOS Devices Including Quasi-Saturation," *IEEE Trans. Electron Devices*, vol. 53, pp. 897-902, 2006.

- [8] K. Joardar, K.K. Gullapulli, C.C. McAndrew, M.E. Burnham, and A. Wild," An improved MOSFET model for circuit simulation," *IEEE Trans. Electron Devices*, vol. 45, pp. 134-148, 1998.

- 9] ATLAS: 2D Device Simulator, SILVACO International 2008.

- Z. Dibi was born in Batna, Algeria, on 1965. He received the degree of Electronics Engineer in 1989, the M.Sc. degree in electronics in 1998 from university of Constantine, the PhD. degree in electronics in 2005 and Habilitation degree in 2007, both from Batna University, Algeria. He is, currently, an associate professor at Batna University. He has published more than 30 journal articles and conference papers. His research interests include: Sensors, Power devices, Microelectronic modeling, Artificial Intelligence computation and Software design.

Dr. Dibi is the Head of Electronics Department and member of the scientific council of the Electronics Department and Faculty of Technology.

F. Djeffal was born in Batna, Algeria, on December 1975. He received the degree of Electronics Engineer in 1998, the M.Sc. degree in electronics in 2002, the PhD. degree in electronics in 2006 and Habilitation degree in 2007, all from Batna University, Algeria. He is, currently, an associate professor at Batna University. He has published more than 80 journal articles and conference papers. He is a referee in some technical journals and conferences such as: Semicon Sciences and Tech, IEEE electron devices, Nanotechnology,... His research interests include: Photovoltaic devices, Nano and Microelectronic modeling, Artificial Intelligence computation and Software design (PSPICE, Cadence, ..).

Dr. Djeffal is a member of the scientific council of the institute of Electronics and member of European Materials Research Society E-MRS from 2007 to 2009. He received an Honor Awards from Batna University in 1998 and 2008, winner of national prize for best scientific publication in 2007, winner of Best paper Award in MADICA'2010, winner of TWAS-AAS-

Microsoft Award in 2010, Marquise's who's who in the world for 2009 and 2011 and Marquise's who's who in Sciences and Engineering in 2011.

N. Lakhdar was born in Batna, Algeria, on September 1980. He received the degree of Electronics Engineer in 2004, the M.Sc. degree in electronics in 2008, both from Batna University, Algeria and is currently working toward the Ph.D. degree on the modeling of III-V based multi-gate transistors at University of Batna, Algeria. He has published more than 14 journal articles and conference papers. His research interests are in fields of Photovoltaic devices, Nano and Microelectronic modeling, Artificial Intelligence and Software design (PSPICE, Silvaco, Cadence ...), with particular emphasis on applications to microwave transistor devices such as the GaN FET. He also has interests in nonlinear simulation algorithms.