# Two Active Elements Based All-Pass Section Suited for Current-Mode Cascading

J. Mohan and S. Maheshwari

Abstract—A new circuit topology realizing a first-order current-mode all-pass filter is proposed using two dual-output second generation current conveyor and two passive components. The circuit possesses low-input and high-output impedance, which makes it ideal for current-mode systems. The proposed circuit is verified through PSPICE simulation results.

Keywords—active filter, all-pass filter, current-mode, current conveyor.

#### I. Introduction

THE circuits with current input, current output are termed as current-mode circuits. Such circuits demand a basic requirement to be of practical use in any larger current-mode system. This requirement is in terms of the input and output impedances which are desirably low and high respectively. Besides, input impedance should be low in comparison to the output impedance in order to avoid loading problems when cascading such circuits to form larger systems. All-pass filters are an important class of analogue signal processing functions with applications in communication and instrumentation systems [1] - [2]. Numerous current-mode all-pass sections (CM-APSs) employing different types of active elements, such as current conveyors and its different variations have been reported in the literature [3]- [22]. Despite a number of first order CM-APSs, there is a need to further explore new topology, keeping the following points into consideration

- Use of optimum passive elements.

- Use of grounded capacitor.

- · Low-input and high-output impedance

- Simple configuration

The technical literature shows that none of the recently reported works provide all the above features simultaneously. Most of the circuits uses single active element and offer high output impedance feature together but employ more than two passive components [3], [6], [12], [16]. Though the circuits described in [5], [9], [14], [18], [19] fall in the separate category of tunable, resistorless realizations, the most recent of these [18], [19] enjoys low input and high output impedance. On the other hand, some of the circuits employ single active element and two passive components [8], [11], [15], [17]. Such circuits aim at realizing the first order all-pass function using optimum number of active and passive components, rather than offering low input and high output impedance. The

vast majority of the circuits offer high output impedance [3], [6], [7], [10], [12], [13], [15]- [17]. Some of the circuits employ floating capacitor [3], [7], [10] - [12], [16], which is not desirable for IC implementation [23]. Though the recently presented circuits in [20], [21] uses three grounded passive components with matching conditions but enjoys low-input and high-output impedances.

This paper presents a new circuit topology which realizes a first-order current-mode all-pass section, with low-input and high-output impedance and employs a grounded capacitor and a resistor. The proposed circuit is based on dual-output plus-type second generation current conveyor (DO-CCII+), which is modified from second generation current conveyor (CCII) [24]. CCII is a device which can operate both in voltage and current-modes, providing flexibility to a variety of analog signal processing circuits. In addition it can offer advantageous feature such as wider signal bandwidth, higher slew-rate, greater linearity and low power consumption. The implementation configuration of the DO-CCII+ is simpler than that of a CCII± (plus and minus type together). Infact, the number of transistors in DO-CCII+ is decreased by four with respect to the CCII± [22]. The cascadable circuit presented in [22] employs two CCII±, one grounded capacitor and one grounded resistor with a feature of high-input and low-output impedances. PSPICE simulation results using 0.5 µm CMOS parameters are given to validate the circuits.

# II. PROPOSED CIRCUIT

A DO-CCII+ with two Z+ outputs is characterized by the following relationship

$$V_X = V_Y, I_{Z1+} = I_{Z2+} = I_X, I_Y = 0$$

(1)

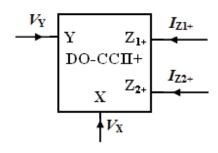

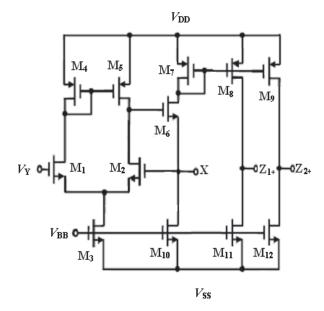

where the suffixes refer to the respective terminals. The DO-CCII+ is characterized by high input impedance at the Y terminal, high output impedance at the Z1+ and Z2+ terminals and low impedance at the X terminal. The symbol and CMOS implementation of the DO-CCII+ are shown in Fig. 1 and 2 [24].

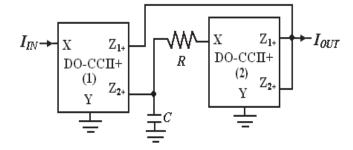

The new proposed circuit using two DO-CCII+ and two passive components is shown in Fig. 3. The circuit is characterized by the following current transfer function

$$\frac{I_{OUT}}{I_{IN}} = -\left(\frac{s - \left(\frac{1}{CR}\right)}{s + \left(\frac{1}{CR}\right)}\right) \tag{2}$$

Equation (2) is the standard current transfer function for a first order all-pass filter with unity gain and frequency dependent phase function  $(\phi)$  with a value  $\phi = -2tan^{-1}(RC)$  and

J. Mohan is with the Department of Electronics and Communication Engineering, Jaypee Institute of Information Technology University, Noida (INDIA) e-mail: jitendramv2000@rediffmail.com.

S. Maheshwari is with the department of Electronics Engineering, Aligarh Muslim University, Aligarh(INDIA)

# World Academy of Science, Engineering and Technology International Journal of Electronics and Communication Engineering Vol:7, No:1, 2013

Fig. 1. Symbol of DO-CCII+

Fig. 2. CMOS Implementation of DO-CCII+

angular pole frequency,  $\omega_o = 1/RC$ . The salient features of the proposed circuit are low-input and high-output impedance, and optimum use of passive components i.e a resistor and a grounded capacitor. These two features are not exhibited together in any of the cited works [2], [3], [5]-[7], [8]-[13], [15]-[17], [20], [21].

# III. NON-IDEAL ANALYSIS

The non-ideal DO-CCII+ is characterized by the following relationships:

$$V_X = \alpha k V_Y, I_{Z1+} = +\beta_{k1} I_X, I_{Z2+} = +\beta_{k2} I_X, I_Y = 0$$

(3)

where,  $\alpha_k(s)$  represent the frequency transfer of the internal voltage follower and  $\beta_{k1}(s)$ ,  $\beta_{k2}(s)$  represent the frequency transfers of the internal current followers of the kth-DO-CCII+, respectively. They can be approximated by first-order low pass functions, which can be considered to have a unity value for frequencies[25]. If this circuit is working at frequencies much less than the corner frequencies of  $\alpha_k(s)$ ,  $\beta_{k1}(s)$  and  $\beta_{k2}(s)$  namely, then  $\alpha_k(s) = 1 - \varepsilon_{kv1}$  and  $\varepsilon_{kv1}$  ( $|\varepsilon_{kv1} \ll 1|$ ) denotes the voltage tracking error from the Y terminal to the X terminal of the kthDO-CCII+;  $\beta_{k1}(s) = \beta_{k1} = 1 - \varepsilon_{ki1}$  and  $\varepsilon_{ki1}$  ( $|\varepsilon_{ki1} \ll 1|$ ) denotes the current tracking

Fig. 3. 2 Proposed current mode cascadable all pass -filter

error from the X terminal to the Z1+ terminal;  $\beta_{k2}(s) = \beta_{k2}$  =1- $\varepsilon_{ki2}$  and  $\varepsilon_{ki2}$  ( $|\varepsilon_{ki2}| \ll 1$ ) denotes the current tracking error from the X terminal to the Z2+ terminal of the kthDO-CCII+. Analysis of the circuit using this description yields the following current transfer function:

$$\frac{I_{OUT}}{I_{IN}} = -\beta_{11} \left( \frac{s - \left[ \frac{\beta_{12}(\beta_{21} + \beta_{22} - \beta_{11}}{\beta_{11}} \right] \left( \frac{1}{CR} \right)}{s + \frac{1}{CR}} \right)$$

(4)

It is easily verified that for the ideal case these gains are unity and (4) reduces to the ideal (2). However, the non-idealities do affect the filter gain, as it now depends on  $\beta_{11}$  but the pole frequency is unaltered by DO-CCII+ non-idealities. The active and passive sensitivities of the proposed CM-APS are derived from (4), which are as follows:

$$S_{C,R}^{\omega_0} = -1$$

$$S_{\alpha_1,\alpha_2,\beta_{11},\beta_{12},\beta_{21},\beta_{22}}^{\omega_0} = 0$$

$$S_{\alpha_1,\alpha_2,\beta_{12},\beta_{21},\beta_{22}}^H = 0$$

$$S_{C,R}^H = 0$$

$$S_{\beta_{11}}^H = 1$$

(5)

From the results it is evident that the sensitivities are within unity in magnitude, thus ensuring a good sensitivity performance.

# IV. EFFECT OF PARASITICS

The practical current conveyors have various parasitics at their Y, Z and X terminals. The main amongst these are the Y and Z terminals parasitic capacitances and the X terminal resistance [25]. The proposed circuit is reanalyzed by considering the above parasitic effects; the following transfer function is obtained

$$\frac{I_{OUT}}{I_{IN}} = -\left(\frac{s - \left(\frac{1}{(C + C_{Z21+})(R + R_{X2})}\right)}{s + \left(\frac{1}{(C + C_{Z21+})(R + R_{X2})}\right)}\right)$$

(6)

where  $C_{Z21+}$  is the parasitic capacitance at the Z2+ terminal of DOCCII+(1) and  $R_{x2}$  is the parasitic resistance at the X-terminal of DOCCII+(2).

# World Academy of Science, Engineering and Technology International Journal of Electronics and Communication Engineering Vol:7, No:1, 2013

From (6), it is seen that the parasitic capacitance at Z2+terminal of conveyor (1) merges with external capacitor (C) and the parasitic resistance at X terminal of conveyor (2) merges with external resistor (R). So, the proposed circuit enjoys a structure where the effects of various parasitics are absorbed by the external components. A slight deviation in pole frequency from the designed values can be expected because of the parasitics.

#### V. SIMULATION RESULTS

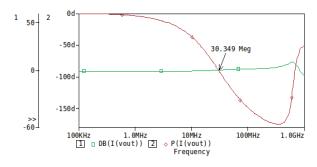

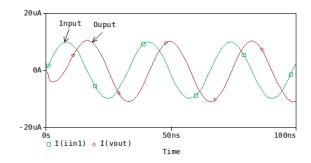

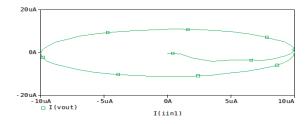

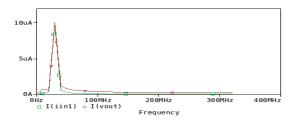

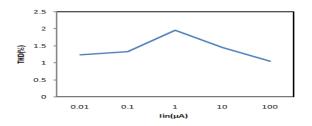

PSPICE simulations were performed using the CMOS realization of DO-CCII+ (Fig. 2) with MOSIS 0.5  $\mu m$  CMOS parameters and aspect ratios as given in Table I and Table II. The supply voltages used were  $\pm 2.3V$  and  $V_{BB} = -1.8V$ . The circuit of Fig. 3 was designed with  $R = 5K\Omega$ , and C = 1pF. The gain and phase responses are shown in Fig. 4, where a pole frequency of 30.349 MHz is obtained. This is close to thetheoretical value of 31.84 MHz. The circuit was next used as a phase shifter introducing a 90° phase shift to a sinusoidal voltage signal of 10  $\mu$ A peak at 31.84 MHz. The input and  $90^{\circ}$  phase-shifted output waveforms are given in Fig. 5 and in the Lissajous pattern of Fig. 6, which verifies the circuit as a phase-shifter. The Fourier spectrum of input signal and output signal are shown in Fig. 7. The total harmonic distortion (THD) variation at the output by varying the amplitude of the input current at a frequency 31.84 MHz is shown in Fig. 8.

TABLE I 0.5  $\mu$ m CMOS PARAMETERS

| NMOS: | LEVEL=3 UO=460.5 TOX=1.0E-8           |  |  |

|-------|---------------------------------------|--|--|

|       | TPG=1 VTO=0.62 JS=1.8E-6 XJ=0.15E-    |  |  |

|       | 6 RS=417 RSH=2.73 LD=0.04E-6          |  |  |

|       | ETA=0 VMAX=130E3 NSUB=1.71E17         |  |  |

|       | PB=0.761 PHI=0.905 THETA=0.129        |  |  |

|       | GAMMA=0.69 KAPPA=0.1 AF=1             |  |  |

|       | WD=0.11E-6 CJ=76.4E-5 MJ=0.357        |  |  |

|       | CJSW=5.68E-10 MJSW=0.302              |  |  |

|       | CGSO=1.38E-10 CDDO=1.38E-             |  |  |

|       | 10 CGBO=3.45E-10 KF=3.07E-28          |  |  |

|       | DELTA=0.42 NFS=1.2E11                 |  |  |

| PMOS: | LEVEL=3 UO= 100 TOX = 1.0E-8 TPG      |  |  |

|       | = 1 VTO =-0.58 JS = 38E-6 XJ = 0.1E-6 |  |  |

|       | RS = 866 RSH = 1.81 LD = 0.03E-6 ETA  |  |  |

|       | =0 VMAX= 113E3 NSUB = 2.08E17 PB      |  |  |

|       | = 0.991 PHI $= 0.905$ THETA $= 0.120$ |  |  |

|       | GAMMA = 0.76 KAPPA =2 AF=1 WD=        |  |  |

|       | 0.14E-6 CJ = 85E-5 MJ = 0.429 CJSW =  |  |  |

|       | 4.67E-10  MJSW = 0.631CGSO = 1.38E-   |  |  |

|       | 10 CGDO = 1.38E-10 CGBO = 3.45E-      |  |  |

|       | 10 KF = 1.08E-29 DELTA = 0.81 NFS =   |  |  |

|       | 0.52E11                               |  |  |

TABLE II

| ASPECT RATIOS USED IN FIG. 3 |            |            |  |

|------------------------------|------------|------------|--|

| MOS Transistors              | $W(\mu m)$ | $L(\mu m)$ |  |

| $M_1, M_2$                   | 20         | 1          |  |

| $M_3$                        | 50         | 2.5        |  |

| $M_4, M_5)$                  | 60         | 2.5        |  |

| $M_6$                        | 40         | 0.5        |  |

| $M_7, M_8, M_9$              | 20         | 2.5        |  |

| $M_{10}, M_{11}), M_{12}$    | 20         | 2.5        |  |

Fig. 4. Simulated Gain and Phase Response for Fig.3

Fig. 5. Input and  $90^o$  phase shifted output at  $31.84Mh_z$

Fig. 6. Lissajous Pattern ( $I_{out}$  against  $I_{IN}$ )for Fig.3

Fig. 7. Fourier spectrum of the input and output signal

#### World Academy of Science, Engineering and Technology International Journal of Electronics and Communication Engineering Vol:7, No:1, 2013

Fig. 8. THD variation with input signal at  $31.84Mh_z$

#### VI. CONCLUSION

This paper presented a new first-order current-mode all-pass filter, employing two DO-CCII+s and two passive components. The circuit enjoys low-input and high-output impedance feature, which is desirable for Current-mode circuits. The circuit uses optimum passive components i.e a resistor and a grounded capacitor. The proposed circuit withgrounded capacitor is suited for IC implementation in CMOS technology and is verified through PSPICE simulations using MOSIS  $0.5\mu m$  CMOS parameters. The new reported circuit further add to the repertoire of CCII based works [21],[22].

#### REFERENCES

- A. S. Sedra, K. C. Smith, "A second generation current conveyor and its applications," *IEEE Trans on Circuit Theory*, vol. 17, pp. 132–134, 1970.

- [2] C. Toumazou, F. J. Lidgey, and D. G. Haigh, Analog IC Design: The Current-Mode Approach. Peter Peregrinus, London, UK 1990

- [3] M. Higashimura, Y. Fukui, "Realization of current-mode allpass networks using a current conveyor," *IEEE Trans. Circuit and System*, vol. 37, pp. 660-661, 1990.

- [4] M. Higashimura, "Current-mode all-pass filters using FTFNs with grounded capacitors," *Electronics Letters*, 27, pp. 1182–1183, 1991.

- [5] T. Tsukutani, M. Higashimura, M. Ishida, S. Tsuiki Y. Fukui, "A general class of current-mode high-order OTA-C filters," *International Journal of Electronics*, vol. 81, no. 6, p. 663–669, 1996.

- [6] A. M. Soliman, "New current mode filters using current conveyors," AEU Int. J. Electron. Commun.," vol. 51, pp. 275–278, 1997.

- [7] A. Toker, S. Ozoguz, O. Cicekoglu, and C. Acar, "Current-mode all-pass filters using current differencing buffered amplifier and a new high-Q band-pass filter configuration," *IEEE Transactions on Circuits and Systems II: Analog and Digital Signal Processing*, vol. 47, no. 9, pp. 949–954, 2000.

- [8] S. Maheshwari and I.A. Khan, "Novel first order all-pass sections using a single CCIII," *International Journal of Electronics*, vol. 88, pp. 773–778, 2001

- [9] S. Maheshwari and I.A. Khan, "Simple first order translinear-C current-mode all-pass sections," *International Journal of Electronics*, vol. 90, pp. 79–85, 2003.

- [10] S. Kilinc and U. Cam, "Current-mode first-order all-pass filter employing single current operational amplifier," *Analog Integrated Circuits and Signal Processing*, vol. 41, no. 1, pp. 47–53, 2004.

- [11] S. Maheshwari, I. A. Khan, "Novel first-order current-mode allpass sections using CCIII," *Active and Passive Elec. Comp.*, vol. 27, p. 111-117, 2004.

- [12] S. Minaei and M. A. Ibrahim, "General configuration for realizing current-mode first-order all-pass filter using DVCC," *International Jour*nal of Electronics, vol. 92, no. 6, pp. 347–356, 2005.

- [13] J. W. Horng, C. L. Hou, C. M. Chang, W. Y. Chung, H. L. Liu, and C. T. Lin, "High output impedance current-mode first-order all-pass networks with four grounded components and two CCIIs," *International Journal of Electronics*, vol. 93, no. 9, pp. 613–621, 2006.

- [14] S. Maheshwari, "A new current-mode current-controlled all-pass section," *Journal of Circuits, Systems and Computers*, vol. 16, no. 2, pp. 181–189, 2007.

- [15] S. Maheshwari, "Novel cascadable current-mode first order all-pass sections," *International Journal of Electronics*, vol. 94, no. 11, pp. 995– 1003, 2007.

- [16] M. Un, F. Kacar, "Third generation current conveyor based current-mode first order all-pass filter and quadrature oscillator," *Istanbul University - Journal of Electrical and Electronics Engineering*, vol. 8, pp. 529-535, 2008

- [17] S. Maheshwari "High output impedance current-mode all-pass sections with two grounded passive components," *IET circuits, devices & system*, vol. 2, pp. 234-242, 2008.

- [18] D. Biolek, V. Biolkova, "All-pass filter employing one grounded capacitor and one active element" *Electronics Letters*, vol. 45, pp. 807-808, 2009

- [19] A. Lahiri and A. Chowdhury, "A novel first-order current-mode all-pass filter using CDTA," *Radioengineering*, vol. 18, no. 3, pp. 300–305, 2009.

- [20] B. Metin, K. Pal, and O. Cicekoglu, "All-pass filter for rich cascadability options easy IC implementation and tunability," *International Journal of Electronics*, vol. 94, no. 11, pp. 1037–1045, 2007.

- [21] J. W. Horng, C. L.Hou, C. Y. Tseng, R. Chang, and D. Y. Yang, "Cascadable Current-Mode First-Order and Second-Order Multifunction Filters Employing Grounded Capacitors," *Active and Passive Electronic Components*, vol. 2012, pp. 1-6, 2012.

- Components, vol. 2012, pp. 1-6, 2012.

[22] S. Minaei, S. and E. Yuce, "All grounded passive elements current-mode All-pass ?lter," Journal of Circuits, Systems and Computers, Vol. 18, no. 1, pp.31–43, 2009.

- [23] M. Bhushan and R. W. Newcomb, "Grounding of capacitors in integrated circuits," *Electronic Letters*, vol. 3, no. 4, pp. 148–149, 1967.

- [24] W. Surakampontorn, V. Riewruja, K. Kumwachara, and K. Dejhan, "Accurate CMOS-based current conveyors," *IEEE Transactions on Instrumentation and Measurement*, vol. 40, no. 4, pp. 699–702, 1991.

- [25] A. Fabre, O. Saaid, and H. Barthelemy, "On the frequency limitations of the circuits based on second generation current conveyors," *Analog Integrated Circuits and Signal Processing*, vol. 7, no. 2, pp. 113–129, 1995

**J. Mohan** obtained his B.Tech. degree from S.R.T.M.University, Nanded in 1997. He got his M.Tech degree from Aligarh Muslim University in 2005 and Ph.D. degree from Uttarakhand Technical University in 2011. He is currently working as a Assistant Professor in the Department of Electronica and Communication at Jaypee Institute of Information Technology, Noida (India). His main areas of interest are current-mode circuits and analog signal processing applications. He has guided 01 Masters Dissertation and 10 projects. He has more than 22 International Journal and conference papers.

S. Maheshwari obtained his B.Sc. (Engg.), M. Tech and Ph.D degrees from Aligarh Muslim University in 1992, 1999 and 2004 respectively. He is currently Associate Professor in the Department of Electronics Engineering of Aligarh Muslim University. He has been engaged in teaching and design of courses related to the design and synthesis of Analog Electronic Circuits and Current-mode Circuits. His research areas include Analog Signal Processing and current-mode circuits. He has published more than 75 research papers, including around 55 International Journal papers and also authored 2 book chapters. He has guided 2 Ph.D.s and more than 25 Masters Dissertations and projects. He has been on the reviewer panel for several top ranked International injurnals