# Effect of Field Dielectric Material on Performance of InGaAs Power LDMOSFET

Yashvir Singh, Swati Chamoli

**Abstract**—In this paper, a power laterally-diffused metal-oxidesemiconductor field-effect transistor (LDMOSFET) on  $In_{0.53}Ga_{0.47}As$  is presented. The device utilizes a thicker field-oxide with low dielectric constant under the field-plate in order to achieve possible reduction in device capacitances and reduced-surface-field effect. Using 2D numerical simulations, performance of the proposed device is analyzed and compared with that of the conventional LDMOSFET. The proposed structure provides 50% increase in the breakdown voltage, 21% increase in transit frequency, and 72% improvement in figure-of-merit over the conventional device for same cell pitch.

Keywords—InGaAs, dielectric, lateral, power MOSFET.

#### I. INTRODUCTION

OW-VOLTAGE (5-40 V) power integrated circuits (PICs) are playing an important role in the portable power management systems such as telecommunication, computer, transportation, and industrial power applications. Power laterally-diffused metal-oxide-semiconductor field-effect transistors (LDMOSFETs) are used as key components in the development of PICs. Presently, silicon is most widely used material in the fabrication of LDMOSFETs due to its ease of fabrication with CMOS process. As the silicon based devices are reaching their performance limit, it is necessary to consider the alternate semiconductor materials for further improvement in the device performance. InGaAs is one of the promising materials which may replace Si in MOSFETs due to its high electron mobility leading to higher current density and lower ON-resistance [1]-[3]. These advantages along with improvements in the fabrication process and oxide-InGaAs interface have led to development of MOSFETs with InGaAs channel for radio-frequency and digital applications [4]-[6]. For the first time, the simulation results on InGaAs power LDMOSFET was reported by Steighner et al. [7]. They have demonstrated that the performance of an InGaAs power LDMOSFET is better as compared to its silicon counterpart. It is important to note that although, the gate field-plate over the drift region is used to enhance the breakdown voltage of a power LDMOSFET but it degrades the high frequency response of the device due to increased gate to drain capacitance. Further, in the reported structure [7], a uniform thickness with same dielectric material was used for gate and field oxides. We propose that the performance of a power

LDMOSFET can be improved by using a thicker field-oxide with high- $\kappa$  and low- $\kappa$  dielectric materials for the gate-oxide and field-oxide, respectively. Therefore, motive of this work is to propose a power LDMOSFET on In<sub>0.53</sub>Ga<sub>0.47</sub>As which consists of greater field-oxide thickness under the field-plate with lesser dielectric constant as compared to the gate-oxide to achieve reduction in the device capacitances as well as redistribution of electric field in the drift region. Using 2D simulations in the device simulator (ATLAS) [8], the performance of the proposed device has been evaluated and compared with that of the conventional In<sub>0.53</sub>Ga<sub>0.47</sub>As power LDMOSFET for the same cell pitch. The proposed device not only exhibits a better trade-off between ON-resistance and breakdown voltage but also improves the transit frequency.

## II. DEVICE STRUCTURE

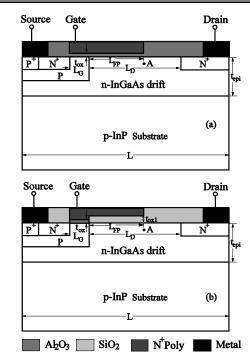

Fig. 1 shows cross-sectional view of the conventional power LDMOSFET (Device1) and the proposed power LDMOSFET structure (Device2) on In<sub>0.53</sub>Ga<sub>0.47</sub>As. The conventional LDMOSFET structure is similar to the device reported in [7] which has a field-plate over the drift region to improve the breakdown voltage. In this structure, Al<sub>2</sub>O<sub>3</sub> with high dielectric constant ( $\kappa = 8.0$ ) material is employed for both the gate-oxide and field-oxide. On the other hand, as shown in Fig. 1 (b), the modified LDMOSFET structure is having a field-plate with thicker field-oxide (tox1) as compared to that of Device1. Further, SiO<sub>2</sub> as a low dielectric constant ( $\kappa = 3.9$ ) material is used for the field-oxide and high- $\kappa$  Al<sub>2</sub>O<sub>3</sub> is placed as the gate-oxide. The larger field-oxide thickness under the field-plate together with a low-к dielectric reduces the device capacitances and hence improves the transit frequency. The modified structure also helps in redistributing the electric field in the drift region causing reduced-surface-field (RESURF) effect in the device. A reduction in peak electric field in the drift region improves the breakdown voltage resulting better trade-off between ON-resistance and breakdown voltage. It may be noted that the peak electric field responsible for the breakdown in both the structures occurs at the end of fieldplate on InGaAs surface (at point 'A' marked in Fig. 1). The optimized structural parameters used in the simulation for both the devices are given in Table I. Note that all structural parameters are kept same for both the devices except fieldoxide thickness (t<sub>ox1</sub>).

Yashvir Singh is with the Department of Electronics & Communication Engineering, G. B. Pant Engineering College, Pauri-Garhwal, Uttarakhand, India (e-mail: om\_ysingh@yahoo.co.in).

Swati Chamoli is with the Department of Electronics & Communication Engineering, G. B. Pant Engineering College, Pauri-Garhwal, Uttarakhand, India (e-mail: schamoli123@gmail.com).

TABLE I

STRUCTURAL PARAMETERS USED IN SIMULATION

Parameter

Symbol

Units

Device1

Device1

| Parameter                | Symbol           | Units            | Device1       | Device2       |

|--------------------------|------------------|------------------|---------------|---------------|

| Cell pitch               | L                | μm               | 4.0           | 4.0           |

| Gate length              | $L_G$            | μm               | 0.5           | 0.5           |

| Field-plate length       | $L_{FP}$         | μm               | 1.2           | 1.2           |

| Drift region length      | L <sub>D</sub>   | μm               | 2.1           | 2.1           |

| Gate oxide thickness     | t <sub>ox</sub>  | μm               | 0.03          | 0.03          |

| Oxide thickness 1        | t <sub>ox1</sub> | μm               | -             | 0.06          |

| Drift epilayer thickness | t <sub>epi</sub> | μm               | 0.65          | 0.65          |

| Drift region doping      | $N_d$            | cm <sup>-3</sup> | $5x10^{16}$   | $5x10^{16}$   |

| P-body doping            | -                | cm <sup>-3</sup> | $1 x 10^{17}$ | $1 x 10^{17}$ |

Fig. 1 Cross-sectional view of (a) Device1 (b) Device2

#### III. SIMULATION RESULTS

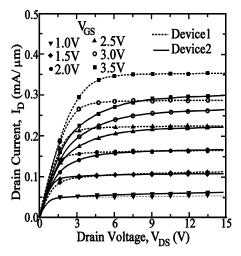

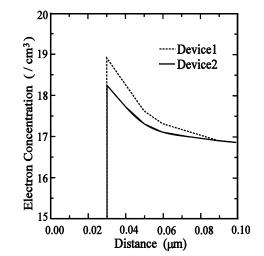

Both the device structures were implemented in device simulator (ATLAS) and 2-D numerical simulations were performed by choosing suitable models for Shockley-Read-Hall, concentration-dependent mobility, electric-fielddependent mobility, and impact ionization [8]. Fig. 2 shows drain characteristics of the Device1 and Device2 at different gate bias voltages. As seen, drain current of both the devices is same below 2.5V gate bias. However, at higher gate voltages, drain current of Device1 is more than that of Device2. This is due to the fact that as gate voltage is increased, an accumulation of electrons occurs in the drift region under the field-plate in Device1 which has thinner field-oxide with highκ dielectric as compared to Device2 having thicker field-oxide with low-k dielectric. It can be better understood from Fig. 3 which gives electron concentration near the surface along a vertical line below gate field-plate in the drift region for both the structures. It is clearly indicated that at same gate bias, V<sub>GS</sub>=5V, the conventional device shows higher electron concentration near the surface as compared to the proposed device. This increased accumulation of electrons in Device1

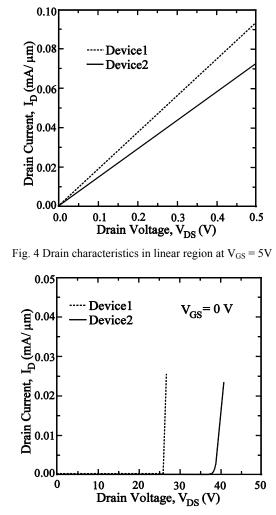

also reduces its ON-resistance. ON-resistance of a MOSFET is taken as the ratio of drain voltage to drain current when device operates in the linear region. Fig. 4 gives drain characteristics in linear region at  $V_{GS} = 5V$  for both the device. Specific ON-resistance of Device1 and Device2 are found to be 20.9 and 27.2 m $\Omega$ -mm<sup>2</sup>, respectively. In other words, specific ON-resistance of Device2 is 30% higher as compared to that of Device1.

Fig. 2 On-state characteristics of Device1 and Device2

Fig. 3 Electron concentration in the drift region along a vertical line near the surface at  $V_{GS} = 5V$  for Device1 and Device2

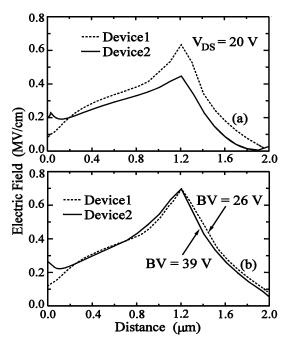

Fig. 5 shows off-state breakdown characteristics of both the devices. At a drift region doping of  $5 \times 10^{16}$  cm<sup>-3</sup>, it is observed that the breakdown voltage of Device2 and Device1 are 39V and 26V, respectively, which provides 50% improvement in the breakdown voltage. The reason for increase in breakdown voltage of the proposed device is reduction in peak electric field in the drift region due to increased field-oxide thickness. Fig. 6 gives the electric field distribution along the surface in the drift region for both the devices. The peak electric field occurs on InGaAs surface in the drift region at point 'A' i.e. at the end of field-plate in both the structures. It can be seen that at  $V_{DS} = 20V$ , peak electric field in the conventional device is

0.65 MV/cm which reduces to 0.40 MV/cm in the proposed structure. However, at breakdown voltages, the peak electric field in both the devices is equal confirming their breakdown at point 'A'. It may be noted that the breakdown voltage of both the devices will be affected by their structural parameters whose optimized values are given in Table I. Although, specific ON-resistance ( $R_{on-sp}$ ) of the proposed device is higher than that of the conventional device but the proposed structure exhibits large improvement in the breakdown voltage ( $V_{br}$ ). Overall effect is that the figure-of-merit (FOM =  $V_{br}^2/R_{on-sp}$ ) of the proposed structure is 72% higher than that of the conventional device i.e. the proposed device provides a better trade-off between ON-resistance and breakdown voltage.

Fig. 5 Breakdown characteristics of Device1 and Device2

Fig. 6 Electric field variation: (a) at  $V_{DS} = 20V$  and (b) at breakdown

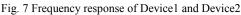

Fig. 8 Capacitance variation for Device1 and Device2

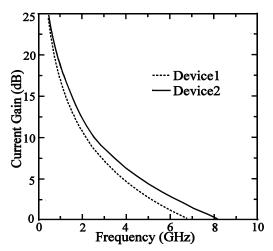

For high frequency power LDMOSFET, it is important to see its current gain variation with frequency to determine transit frequency of the device. Transit frequency (f<sub>T</sub>) of a MOSFET is expressed as;  $f_T = g_m/(2\pi (C_{gs} + C_{gd}))$ , where  $g_m$  is the transconductance,  $C_{gs}$  is gate-source capacitance, and  $C_{gd}$ is gate-drain capacitance. In order to improve the transit frequency, device capacitances should be minimized. Fig. 7 gives frequency response of both the devices. The transit frequency of Device1 and Device2 are found to be 6.7 and 8.1 GHz, respectively. In other words, transit frequency of Device2 is 21% higher as compared to Device1. This improvement in frequency response of the proposed structure is due to reduced  $C_{gs}$  and  $C_{gd}.$  These capacitances of both the structures are compared in Fig. 8. It is observed that the proposed device provides much lower capacitances due to thicker field-oxide with low-k dielectric as compared to the conventional device.

### IV. CONCLUSION

An  $In_{0.53}Ga_{0.47}As$  based power LDMOSFET structure is presented. The proposed device uses a thicker field-oxide with low dielectric constant material to improve the performance. Based on 2D numerical simulations, it is demonstrated that the proposed structure provides 50% increase in breakdown voltage, 21% increase in transit frequency and 72% improvement in figure-of-merit when compared with the conventional LDMOSFET. However, drain current and ONresistance of the proposed device degrade at higher gate bias due to formation of an accumulation layer in the conventional device. The proposed structure is a suitable power MOSFET for power integrated circuits and high frequency power amplifier applications.

#### References

- J. C. Lee, and H. Zhao, "IIIV MOSFETs with ALD High-k Gate Dielectrics," Wiley-VCH Verlag GmbH & Co. KGaA, 2012, pp. 433– 470.

- [2] S. Datta, A. V. Thathachary, L. Liu, E. Hwang, A. Agrawal, and N. Agrawal, "III-V Compound Semiconductor Field Effect Transistors for Low Power Digital Logic," *ECS Transactions*, vol. 53(3), pp. 3-14, 2013.

- [3] T. Homma, K. Hasegawa, H. Watanabe, S. Hara, and H. I. Fujishiro, "Comparative study on nano-scale III-V MOSFETs with various channel materials using quantum-corrected Monte Carlo simulation," *Physica Status Solidi (c)*, vol. 9(2), pp. 346–349, 2012.

[4] S. Tewari, A. Biswas, and A. Mallik, "Study of InGaAs-Channel

- [4] S. Tewari, A. Biswas, and A. Mallik, "Study of InGaAs-Channel MOSFETs for Analog/Mixed-Signal System-on-Chip Applications," *IEEE Electron Device Lett*, vol. 33, pp. 372–374, Mar. 2012.

- [5] M. Egard, L. Ohlsson, M. Arlelid, K. M. Persson, B. M. Borg, F. Lenrick, R. Wallenberg, E. Lind, and L. E. Wernersson, "High-Frequency Performance of Self-Aligned Gate-Last Surface Channel In<sub>0.53</sub>Ga<sub>0.47</sub>As MOSFET," *IEEE Electron Device Lett.*, vol. 33, pp. 369–371, Mar. 2012.

- [6] A. T. M.G. Sarwar, M. R. Siddiqui, M. M. Satter, and A. Haque, "On the Enhancement of the Drain Current in Indium-Rich InGaAs Surface-Channel MOSFETs," *IEEE Transactions on Electron Devices*, vol. 59, pp. 1653–1660, Jun. 2012.

- [7] J. B. Steighner, J. S. Yuan, and Y. Liu, "Simulation and analysis of InGaAs power MOSFET performances and reliability," *IEEE Trans. Electron Devices*, vol. 58, pp. 180–189, Jan. 2011.

- [8] ATLAS User's manual: Device simulation software, Silvaco Int., Santa Clara, CA, (2010).