# Switching Behaviors of HfO<sub>2</sub>/NiSi<sub>x</sub> Based RRAM

Z. X. Chen, Z. Fang, X. P. Wang, G. -Q. Lo, D. -L. Kwong, and Y. H. Wu

**Abstract**—This paper presents a study of Ni-silicides as the bottom electrode of HfO<sub>2</sub>-based RRAM. Various silicidation conditions were used to obtain different Ni concentrations within the Ni-silicide bottom electrode, namely Ni<sub>2</sub>Si, NiSi, and NiSi<sub>2</sub>. A 10nm HfO<sub>2</sub> switching material and 50nm TiN top electrode was then deposited and etched into 500nm by 500nm square RRAM cells. Cell performance of the Ni<sub>2</sub>Si and NiSi cells were good, while the NiSi<sub>2</sub> cell could not switch reliably, indicating that the presence of Ni in the bottom electrode is important for good switching.

**Keywords**—HfO<sub>2</sub>-based, Ni-silicide, NiSi, resistive RAM (RRAM).

#### I. INTRODUCTION

RESISTIVE RAM (RRAM) has been researched extensively in recent years to address scaling issues in flash memories based on charge-trapping non-volatile memory (NVM) [1]-[12]. The fast program/erase and low operating voltages make it suitable either for embedded NVM or standalone NVM using standard CMOS process. Furthermore, the simple metal-insulator-metal structure of the RRAM allows for high density integration.

A popular choice of top metal electrode and dielectric is TiN/HfO<sub>2</sub> [10]-[12]. Oxygen vacancies are believed to form within the HfO<sub>2</sub> due to the applied electric field during SET process as the TiN acts as an oxygen gettering layer. The oxygen is then released back into the HfO<sub>2</sub> during the RESET process.

This work presents a study of Ni-silicide as the bottom electrode, with HfO<sub>2</sub> as dielectric and TiN as top electrode. Various silicidation conditions were used to form Ni-silicides with different Ni concentrations, namely Ni<sub>2</sub>Si, NiSi, and NiSi<sub>2</sub>. It was found that the Ni<sub>2</sub>Si and NiSi cells performed well, while the NiSi<sub>2</sub> cell could not switch reliably, indicating that the presence of Ni in the bottom electrode is important for good switching.

## II. DEVICE FABRICATION

Devices were fabricated on *p*-type (~10<sup>15</sup> cm<sup>-3</sup>) 8-inch silicon wafers. The bottom electrode (BE) was first formed through silicidation of the silicon substrate under the various conditions listed in Table I. First, Ni is deposited and then the first silicidation performed at high temperatures. Excess Ni is

then removed by wet etch in  $H_2SO_4$ : $H_2O_2$ : $H_2O$  solution after the first anneal. A second anneal is done after the Ni removal for D3 only. After silicidation, 10nm  $HfO_2$  switching oxide and 50nm TiN top electrode (TE) were deposited through physical vapor deposition (PVD). The TE was then patterned into 500nm by 500nm patterns by lithography using a 248nm KrF scanner. The TE is then dry etched using  $Cl_2$  chemistry.  $SiO_2$  is then deposited as pre-metal deposition (PMD) and contact holes etched to contact TE and BE. This is followed by metallization with Al using TaN as a barrier metal.

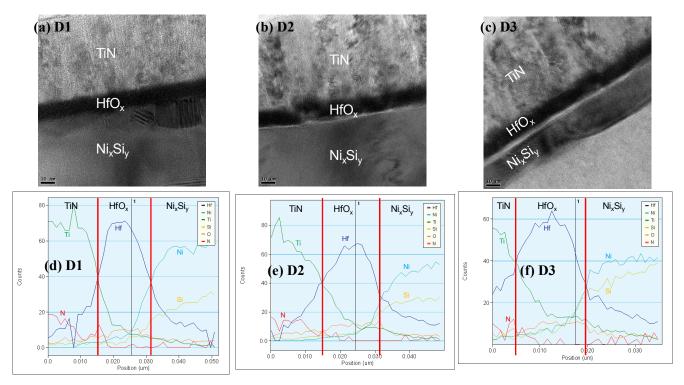

Figs. 1 (a) to (c) show the transmission electron micrographs (TEM) images of D1-D3, respectively. Fig. 1 (d) to (f) shows the energy dispersive x-ray spectroscopy (EDX) line scans of D1-D3, respectively. It is clear from the EDX that the Ni concentration is highest for D1 and lowest for D3, with D2 having a concentration between the two.

## III. RESULTS AND DISCUSSION

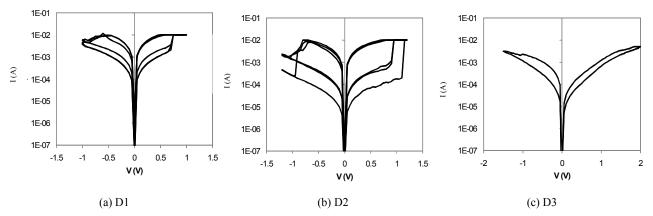

Figs. 2 (a) to (c) show the typical switching characteristics of D1-D3, respectively. It can be seen that the switching current tends to be high (>1mA). This could indicate a large filament is formed during the forming/SET. Also, the SET voltages are fairly low (~0.6V for D1 and ~0.8V for D2). Unfortunately, D3 fails to switch after the forming process, which could be due to the low Ni concentration.

The memory window for D1 and D2 is >10x, which should be sufficient to resolve both low resistance state (LRS) and high resistance state (HRS). D2 appears to have a slightly larger memory window, with one RESET cycle even causing the HRS to drop lower than the typical HRS level, resulting in nearly a 100x memory window. However, this phenomena was found to only occur sometimes. Although D2 was found to be the best performing cell, it should be noted that the Ni-silicide surface of the BE is quite rough, as can be seen in Fig. 1 (b). This could result in some switching non-uniformity. This could also be the reason for the large drop in current during that one RESET process. Conversely, this could also possibly result in over SET or negative parasitic SET.

TABLE I Nickel Silicdation Conditions for Bottom Electrodes

| NICKEL SILICDATION CONDITIONS FOR BOTTOM ELECTRODES |              |              |               |

|-----------------------------------------------------|--------------|--------------|---------------|

| Device                                              | D1           | D2           | D3            |

| Ni thickness                                        | 30nm         | 30nm         | 15nm          |

| Silicidation1st step                                | 300°C, 30sec | 440°C, 30sec | 220°C, 120sec |

| Silicidation 2 <sup>nd</sup> step                   | None         |              | 440°C, 30sec  |

Z. X. Chen, Z. Fang, X. P. Wang, G. -Q. Lo, and D. -L. Kwong are with the Institute of Microelectronics, A\*STAR (Agency for Science, Technology and Research), 11 Science Park Road, Singapore Science Park II, Singapore 117685 (phone: +65 6770-5633; e-mail: chenzx@ime.a-star.edu.sg).

Z. X. Chen and Y. H. Wu are with the department of Electrical and Computer Engineering, National University of Singapore, Singapore 119077.

## World Academy of Science, Engineering and Technology International Journal of Electronics and Communication Engineering Vol:7, No:9, 2013

Fig. 1 (a)-(c) Transmission electron micrographs (TEM) and (d)-(f) electron dispersive x-ray spectroscopy (EDX) line scans from TiN to Nisilicide of the various devices, D1-D3, respectively

Fig. 2 (a)-(c) Switching I-V characteristics of the various devices, D1-D3, respectively

## IV. CONCLUSION

A study of Ni-silicide as the bottom electrode of RRAM is presented. HfO<sub>2</sub> was the dielectric and TiN was the top electrode. Various silicidation conditions were used to form Ni-silicides with different Ni concentrations, namely Ni<sub>2</sub>Si, NiSi, and NiSi<sub>2</sub>. It was found that the Ni<sub>2</sub>Si and NiSi cells performed well, while the NiSi<sub>2</sub> cell could not switch reliably, indicating that the presence of Ni in the bottom electrode is important for good switching.

#### ACKNOWLEDGMENT

This work was supported by Future Data Center Technologies Thematic Strategic Research Programme: NVM based on integration of PCRAM and RRAM cells with ultra scaled vertical Si nanowire devices (SERC Grant No: 1121720016).

## REFERENCES

- [1] Y. Y. Chen, G. Pourtois, X. P. Wang, C. Adelmann, L. Goux, B. Govoreanu, L. Pantisano, S. Kubicek, L. Altimime, M. Jurczak, J. A. Kittl, G. Groeseneken, and D. J. Wouters, "Switching by Ni filaments in a HfO2 matrix: a new pathway to improved unipolar switching RRAM," *IEEE International Memory Workshop (IMW)*, 2011, pp. 1-4.

- [2] I. G. Baek, D. C. Kim, M. J. Lee, H. J. Kim, E. K. Yim, M. S. Lee, J. E. Lee, S. E. Ahn, S. Seo, J. H. Lee, J. C. Park, Y. K. Cha, S. O. Park, H. S. Kim, I. K. Yoo, U. I. Chung, J. T. Moon, and B. I. Ryu, "Multi-layer cross-point binary oxide resistive memory (OxRRAM) for post-NAND storage application," in *IEDM Tech. Dig.*, 2005, pp. 750–753.

- [3] C. H. Wang, Y.-H. Tsai, K.-C. Lin, M.-F. Chang, Y.-C. King, C.-J. Lin, S.-S. Sheu, Y.-S. Chen, H.-Y. Lee, F. T. Chen, and M.-J. Tsai, "Threedimensional 4F2 ReRAM cell with CMOS logic compatible process", in *IEDM Tech Dig.*, 2010, pp. 664-667.

- [4] H. Y. Lee, P. S. Chen, T. Y. Wu, Y. S. Chen, C. C. Wang, P. J. Tzeng, C. H. Lin, F. Chen, C. H. Lien, and M.-J. Tsai, "Low power and high speed bipolar switching with a thin reactive Ti buffer layer in robust HfO2 based RRAM", in *IEDM Tech Dig.*, 2008, pp. 297-300.

## World Academy of Science, Engineering and Technology International Journal of Electronics and Communication Engineering Vol:7, No:9, 2013

- [5] Y. H. Tseng C.-E Huang, C.-H. Kuo, Y.-D. Chih, C. J Lin, "High density and ultra small cell size of contact ReRAM (CR-RAM) in 90nm CMOS logic technology and circuits", in *IEDM Tech Dig.*, 2009, pp. 109-112.

- [6] C. H. Ho, C.-L. Hsu, C.-C. Chen, J.-T. Liu, C.-S. Wu, C.-C. Huang, C. M. Hu, and F.-L. Yang, "9nm half-pitch functional resistive memory cell with <1μA programming current using thermally oxidized substoichiometric WOx film". in *IEDM Tech Dig.* 2010, pp. 436-439.

- stoichiometric WOx film", in *IEDM Tech Dig.*, 2010, pp. 436-439.

[7] C. H. Cheng, C. Y. Tsai, Albert Chin, and F. S. Yeh, "High performance ultra-low energy RRAM with good retention and endurance", in *IEDM Tech Dig.*, 2010, pp. 448-451.

- [8] X. A. Tran, B. Gao, J. F. Kang, L. Wu, Z. R. Wang, Z. Fang, K. L. Pey, Y. C. Yeo, A. Y. Du, B. Y. Nguyen, M. F. Li and H. Y. Yu, "High performance unipolar AlOy/HfOx/Ni based RRAM compatible with Si diodes for 3D application", in VLSI Symp. Tech. Dig., 2011, p. 44-45.

[9] U. Russo, D. Ielmini, C. Cagli, and A. L. Lacaita, "Filament conduction

- [9] U. Russo, D. Ielmini, C. Cagli, and A. L. Lacaita, "Filament conduction and reset mechanism in NiO-based resistive-switching memory (RRAM) devices", *IEEE Trans. Elec. Dev.*, vol. 56, pp. 186-192, 2009.

- [10] G. Bersuker, D. C. Gilmer, D. Veksler, J. Yum, H. Park, S. Lian, L. Vandelli, A. Padovani, L. Larcher, K. McKenna, A. Shluger, V. Iglesias, M. Porti, M. Nafria, W. Taylor, P. D. Kirsch, and R. Jammy, "Metal oxide RRAM switching mechanism based on conductive filament microscopic properties," in *IEDM Tech. Dig.*, 2010, pp. 456–459.

[11] Z. Fang, H. Y. Yu, W. J. Liu, Z. R. Wang, X. A. Tran, B. Gao, and J. F.

- [11] Z. Fang, H. Y. Yu, W. J. Liu, Z. R. Wang, X. A. Tran, B. Gao, and J. F. Kang, "Temperature Instability of Resistive Switching on HfOx-Based RRAM Devices," *IEEE Elec. Dev. Lett.*, vol. 31, no. 5, pp. 476-378, May 2010.

- [12] X. A. Tran, B. Gao, J. F. Kang, X. Wu, L. Wu, Z. Fang, Z. R. Wang, K. L. Pey, Y. C. Yeo, A. Y. Du, M. Liu, B. Y. Nguyen, M. F. Li, and H. Y. Yu, "Self-rectifying and forming-free unipolar HfOx based-high performance RRAM built by fab-availabe materials," in *IEDM*, 2011, pp. 31.2.1-31.2.4.