# Star-Hexagon Transformer Supported UPQC

Yash Pal, A.Swarup and Bhim Singh

Abstract—A new topology of unified power quality conditioner (UPQC) is proposed for different power quality (PQ) improvement in a three-phase four-wire (3P-4W) distribution system. For neutral current mitigation, a star-hexagon transformer is connected in shunt near the load along with three-leg voltage source inverters (VSIs) based UPQC. For the mitigation of source neutral current, the uses of passive elements are advantageous over the active compensation due to ruggedness and less complexity of control. In addition to this, by connecting a star-hexagon transformer for neutral current mitigation the over all rating of the UPQC is reduced. The performance of the proposed topology of 3P-4W UPOC is evaluated for power-factor correction, load balancing, neutral current mitigation and mitigation of voltage and currents harmonics. A simple control algorithm based on Unit Vector Template (UVT) technique is used as a control strategy of UPQC for mitigation of different PQ problems. In this control scheme, the current/voltage control is applied over the fundamental supply currents/voltages instead of fast changing APFs currents/voltages, thereby reducing the computational delay. Moreover, no extra control is required for neutral source current compensation; hence the numbers of current sensors are reduced. The performance of the proposed topology of UPQC is analyzed through simulations results using MATLAB software with its Simulink and Power System Block set toolboxes.

**Keywords**—Power-factor correction, Load balancing, UPQC, Voltage and Current harmonics, Neutral current mitigation, Starhexagon transformer.

## I. Introduction

THE AC distribution systems are facing severe PQ I problems such as high reactive power burden, voltage and current harmonics, poor power-factor, voltage sag, swells and voltage dip etc. There are various reasons behind this; some of these are increasing use of non-linear and poor-power factor loads at commercial, industrial and domestic purposes. Different devices such as rectifiers, inverters, adjustable speed drives, computer power supplies, furnaces and traction drives lead to non-linear current waveforms and hence degrade the quality of power. The quality degradation leads to low powerfactor, low efficiency, overheating of transformers and so on [1].In addition to this the load on a 3P-4W distribution system hardly found balanced. Because of this there is an excessive neutral current of fundamental and as well harmonic frequencies in the neutral conductor [2-3]. The power quality at the distribution system is limited by various standards [4-5] lay down by different agencies. Under the present deregulated

Yash Pal is with the National Institute of Technology, Kurukshetra, Haryana, India. (Phone: 01744-233400; fax: 01744-238050; e-mail: yash\_pal1971@ yahoo.com).

A. Swarup is with the National Institute of Technology, Kurukshetra, Haryana, India. (e-mail: aswarup@nitkkr.ac.in).

Bhim Singh is with the Electrical Engineering Department, Indian Institute of Technology, N.Delhi, India. (e-mail: bhimsinghiitd@gmail.com).

power market, adherence to different power quality standards has become a figure of merit for the utilities.

Custom Power Devices (CPDs) has been reported as a remedy for improving the quality and reliability of electric power distribution systems. D-statcom[6], DVR[7] and UPQC[8-15] are mainly three CPDs. The D-statcom is a shunt device, which mitigates current based distortions, while DVR is a series device, which is responsible for voltage based distortions. The UPQC is a combination of shunt and series APFs, which can provide balance, distortion-free and constant magnitude power to the sensitive load. In addition to this, it restricts the harmonic, unbalance, and reactive power demanded by the load and hence make the overall power distribution system more reliable and healthy [8-15].

Different topologies of 3P-4W UPQC are reported in literature for neutral current compensation along with other PQ problems. Some of these are three-leg VSI with split capacitor[9],three-single phase VSI[12],four-leg VSI[10],[14], current source inverter [15] etc. In case of split capacitor topology an extra control loop is required to maintain a zero voltage error difference between both the capacitor voltages, while three-single phase VSIs topology is bulky in nature, hence not attractive. Out of these reported topologies, the four-leg VSI topology is most popular, but has the disadvantages of greater number of semiconductor switches, complexity of control, etc.

Different applications of star-hexagon transformer are reported in literature [16-17]. For the mitigation of source neutral current, the uses of passive elements are advantageous over the active compensation due to ruggedness and less complexity of control. For the mitigation of source neutral current along with other current based distortions, the integration of readily available three-leg VSI with starhexagon transformer has been reported in literature for threefour-wire D-Statcom[6]. Unfortunately, performance of the star- hexagon transformer for neutral current mitigation is affected to an extent under distorted or unbalanced source voltages, which is very common in practice. As the UPOC takes care of both voltage and current based distortions simultaneously; hence the integration of starhexagon transformer for neutral current compensation with UPQC is more justified.

This paper proposes a new topology/structure for 3P4W UPQC, in which a star-hexagon transformer is connected near the load along with readily available three-leg VSI of shunt APF. The hexagon connected secondary winding of the transformer provides a path for the zero sequence fundamental current and harmonics currents and hence mitigates the source neutral current. In addition to this, by connecting a star-hexagon transformer in shunt on the load side, the rating of the UPQC is reduced due to elimination of a fourth leg compared to three-phase four-leg VSI based UPQC. The

performance of this proposed structure/topology is evaluated for power-factor correction, source neutral current compensation, load balancing, current harmonic mitigation and voltage harmonic mitigation.

Different control strategies reported in the literature to determine the reference values of the voltage and the current of three-phase four-wire UPQC, the most common are the ptheory[9],modified single-phase p-q synchronous reference frame(SRF) theory[11], symmetrical component transformation [12],and unit technique(UTT) [13] etc. Apart from this one cycle control (OCC) [14] (without reference calculation) is also used for the control of three-phase, four-wire UPOC. In this paper a simplified control algorithm based UTT is used as a control scheme for the UPQC system. In this control scheme, the current/voltage control is applied over the fundamental supply changing currents/voltages instead of fast currents/voltages, thereby reducing the computational delay .Moreover, by connecting a star-hexagon transformer on load side, no extra control is required for source neutral current, hence numbers of current sensors are reduced.

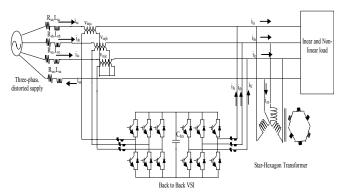

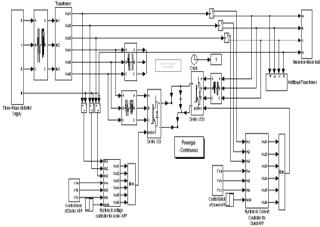

Fig. 1 Detailed Configuration of Proposed 3P-4W UPQC

### II. SYSTEM CONFIGURATION AND DESIGN

Fig. 1 shows the proposed topology of 3P-4W UPQC, which is feeding a combination of linear and non-linear unbalanced load. The series and shunt APFs are realized using two readily available three-leg VSIs. The dc link of both APF is connected to a common dc link capacitor. The series APF is connected between the supply and load terminals using three single phase transformers with turn's ratio of 5:1. The primary winding of these transformer are star connected and the secondary windings are connected in series with the threephase supply. In addition to provide the required injecting voltages, these transformers are used to filter the switching ripple content in the series APF. A small capacity rated R-C filter is connected in parallel with the secondary of each series transformer to eliminate the high switching ripple content in the series APF injected voltage. The voltage source inverters for both the APFs are implemented with Insulated gate Bipolar Transistors ( IGBTs). In Fig.1 ( $i_{sa}$ ,  $i_{sb}$ ,  $i_{sc}$ ), ( $i_{la}$ ,  $i_{lb}$ ,  $i_{lc}$ ) and (i<sub>fa.</sub> i<sub>fb.</sub>, i<sub>fc.</sub>), represent the source currents, load currents and shunt APF currents in phase a, b and c respectively. The source neutral current, load neutral current and neutral current of the additional connected transformers are represented by  $i_{sn}$ ,  $i_{ln}$  and  $i_{Tn}$ , respectively. The injected voltages by the series APF in phase a, b and c is represented by  $v_{inja}$ ,  $v_{injb}$  and  $v_{inje}$ , respectively.

In Fig.1, a star-hexagon transformer is connected in shunt near the load for the mitigation of the source neutral current. The hexagon connected secondary winding of the transformer provides a path for the zero sequence fundamental current and harmonics currents, hence the neutral current is effectively compensated. The load under consideration is a combination of linear and non-linear load. Two single-phase lagging power-factor loads are taken as unbalanced linear load, where as a three-phase diode bridge rectifier with a resistive load on dc side is considered as a non-linear load. The values of the circuit parameters and load under consideration are given in Appendix. The selection criteria of interfacing inductor, dc capacitor, ripple filter and star-hexagon transformer is given in the following section.

## A. DC Capacitor voltage

The value of the common link DC bus voltage of back to back connected VSIs of the UPQC depends on the instantaneous energy available to the UPQC [18]. For a VSI the DC link voltage is defined as

$$V_{dc} = \frac{2\sqrt{2}V_{LL}}{\sqrt{3}m} \tag{1}$$

where m is the modulation index and  $V_{LL}$  is the ac line out voltage of UPQC. Considering modulation index as 1 and for line to line voltage ( $V_{LL}$ =415 V), the  $V_{dc}$  obtained is 677.69 V and is selected as 700 V.

## B. DC Bus voltage

The value of dc capacitor ( $C_{dc}$ ) of back to back connected VSIs of the UPQC depends on the change of DC voltage during increase and decrease of the load. Using the principle of energy conservation, the equation [20] for  $C_{dc}$  is as follows

$$\frac{1}{2}C_{dc}\left[\left(V_{dc}^{2}\right)-\left(V_{dd}^{2}\right)\right]=3V(\alpha I)t\tag{2}$$

where  $V_{\text{dc}}$  is the reference dc voltage and  $V_{\text{dc1}}$  is the minimum voltage level of dc bus,  $\alpha$  is the overloading factor, V is the phase voltage, I is the phase current, and t is the time by which the dc bus voltage is to be recovered.

Considering the minimum voltage level of dc the bus,  $V_{dc1}$ =690 V,  $V_{dc}$ =700 V, V=415/sqrt (3) =239.60 V, I=25.40 A, t=350 $\mu$ s,  $\alpha$ =1.2, the calculated value of  $C_{dc}$  is 2340 $\mu$ F.Hence  $C_{dc}$  is selected as 3000  $\mu$ F.

## C.AC Inductor

The selection of the ac inductance ( $L_f$ ) of VSI depends on the current ripple  $i_{cr,p-p}$ , switching frequency  $f_s$ , dc bus voltage ( $V_{dc}$ ), and  $L_f$  is given as [18]

$$L_f = \frac{\sqrt{3}mV_{dc}}{12 \alpha f_s i_{cr(p-p)}}$$

(3)

where m is the modulation index and  $\alpha$  is the overload factor. Considering,  $i_{cr,p-p}$ =2.5%,  $f_s$ =10 KHz, m=1, $V_{dc}$ =700 V,  $\alpha$ =1.2, the  $L_f$  value is calculated to be 4.88 mH. A round-off value of  $L_f$  of 5 mH is selected in this work.

## D.Ripple Filter

A low-pass first-order filter at half the switching frequency is used to filter the high-witching frequency noise from the injected voltage of series APF. Considering a low impedance of  $8.1\Omega$  for the harmonic voltage at half the switching frequency 10 KHz /2=5 KHz, the ripple filter capacitor is designed as  $C_f$  =5 $\mu$ F. A series resistance ( $R_f$ ) of 7  $\Omega$  is included in series with the capacitor ( $C_f$ ). The impedance is found to be  $638\Omega$  at fundamental frequency, which is sufficiently large, and, hence, the ripple filter draws negligible fundamental current.

## E. Design of Star-hexagon transformer [6]

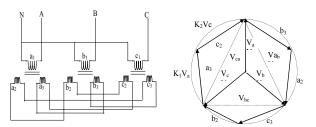

The hexagon-connected secondary winding of the starhexagon transformer provides a path for the zero sequence fundamental currents and hence the source neutral current is mitigated. The connection diagram of star-hexagon transformer is shown in Fig. 2(a), while Fig. 2 (b) shows the phasor diagram.

Fig. 2(a) Star-hexagon transformer. (b)Phasor diagram

From the phasor diagram the  $V_{ca}$  can be written in terms of phase voltages  $V_a$  and  $V_c$  are the per equation (4).

$$V_{ca} = K_1 V_a - K_2 V_c \tag{4}$$

where  $K_1$  and  $K_2$  are the fraction of winding in the phases. Considering phase 'a' as reference and putting the values of  $V_a$ ,  $V_c$  and  $V_{ca}$  in equation(7), we gets the following relationship

$$\sqrt{3}V \angle 30^{\circ} = K_1 V \angle 0^{\circ}V - K_2 V \angle -120^{\circ}$$

(5)

One gets,  $K_1 = K_2 = 1$

For a line to line voltage of 415 V, we gets

$$V_a = V_b = V_c = \frac{415}{\sqrt{3}} = 239.6V$$

Hence, three single-phase transformers with turn's ratio 1:1 of rating 5KVA, 240 V/240 V/240 V are selected.

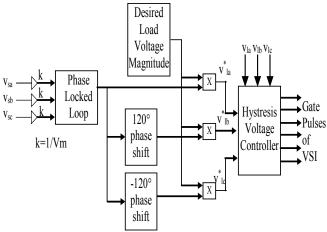

#### III. CONTROL SCHEME OF SERIES APF

A simple control algorithm based on UVT is used to control the series APF of proposed topology. The series is controlled in such a way that it injects voltages ( $v_{inja}$ ,  $v_{injb}$  and  $v_{injc}$ ), which cancel outs the distortions present in the supply voltages ( $v_{sa}$ ,  $v_{sb}$  and  $v_{sc}$ ), thus making the voltages at PCC ( $v_{la}$ ,  $v_{lb}$  and  $v_{lc}$ ) perfectly sinusoidal with the desired amplitude. In other words, the sum of supply voltage and the injected series filter voltage makes the desired voltage at the load terminals. The control strategy for the series APF is shown in Fig. 3. Three-phase distorted supply voltages are sensed and given to

PLL which generates two quadrature unit vectors ( $\sin wt$ ,  $\cos wt$ ). The in-phase sine and cosine outputs from the PLL are used to compute the supply in phase,  $120^{\circ}$  displaced three unit vectors ( $u_a$ ,  $u_b$   $u_c$ ) using eqn.(6) as:

$$\begin{bmatrix} u_{a} \\ u_{b} \\ u_{c} \end{bmatrix} = \begin{bmatrix} 1 & 0 \\ -\frac{1}{2} & -\frac{\sqrt{3}}{2} \\ -\frac{1}{2} & \frac{\sqrt{3}}{2} \end{bmatrix} \begin{bmatrix} \sin \theta \\ \cos \theta \end{bmatrix}$$

(6)

The computed three in-phase unit vectors then multiplied with the desired peak value of the PCC phase voltage  $(V^*_{lm})$ , which becomes the three-phase reference PCC voltages as:

$$\begin{bmatrix} v_{la}^* \\ v_{lb}^* \\ v_{lc}^* \end{bmatrix} = V_{lm}^* \begin{bmatrix} u_a \\ u_b \\ u_c \end{bmatrix}$$

$$\begin{bmatrix} u_b \\ u_c \end{bmatrix}$$

Desired

Fig. 3(a) Control Scheme of Series APF

The desired peak value of the PCC voltage under consideration is 338V (=415sqrt (2)/sqrt(3)). The computed voltages from reference voltages from eqn.(2) are then given to the hysteresis voltage controller along with the sensed three phase PCC voltages( $v_{la}$ ,  $v_{lb}$  and  $v_{lc}$ ). The output of the hysteresis controller is switching signals to the six switches of the VSI of series APF. The hysteresis controller generates the switching signals such that the voltage at PCC becomes the desired sinusoidal reference voltage. Therefore, the injected voltage across the series transformer through the ripple filter cancels out the harmonics present in the supply voltage.

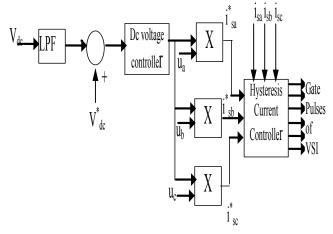

#### IV. CONTROL SCHEME OF SHUNT APF

The control algorithm for shunt APF consists of the generation of three-phase reference supply currents ( $i^*_{sa}$ ,  $i^*_{sb}$  and  $i^*_{sc}$ ) and it is depicted in Fig.4. This algorithm uses supply in-phase, 120° displaced three unit vectors computed in eqn.(3). The amplitude of the reference supply current( $I^*_{sp}$ ) is computed from the comparison of average and the reference value of the dc bus voltage of the back to back connected VSIs results in voltage error, which is fed to a proportional integral(PI) controller. The out put of the PI controller is taken as the reference amplitude ( $I^*_{sp}$ ) of the supply currents. The three in-phase reference supply currents are computed by multiplying their amplitude ( $I^*_{sp}$ ) and in-phase unit current vectors as:

$$\begin{bmatrix} i_{sa}^* \\ i_{sb}^* \\ i_{sc}^* \end{bmatrix} = I_{sp}^* \begin{bmatrix} u_a \\ u_b \\ u_c \end{bmatrix}$$

(8)

The computed three-phase supply reference currents are compared with the sensed supply currents and are given to a hysteresis current controller to generate the switching signals to the switches of the shunt APF which makes the supply currents fallow its reference values. In this control scheme, the current control is applied over the fundamental supply currents instead of the fast changing APF currents, thereby reducing the computational delay. With the integration of starhexgon transformer, no extra control is required for the mitigation of source neutral current; hence numbers of current sensors are reduced.

Fig.4 Control Scheme of Shunt APF

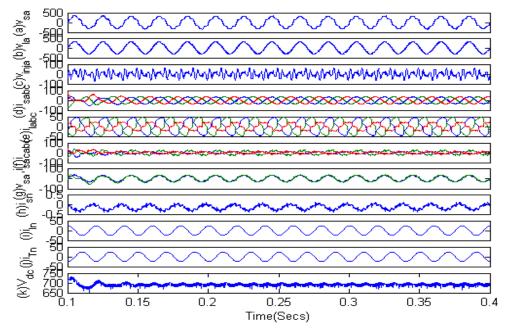

Fig.5 MATLAB model of proposed 3P-4W UPQC

## V.RESULTS AND DISCUSSION

The developed model of the proposed UPQC system using MATLAB/SIMULINK environment is shown in Fig.5. The distortion in utility voltage is introduced deliberately by injecting 5<sup>th</sup>, 7<sup>th</sup> order voltage harmonics along with the fundamental. The combination of unbalanced linear and nonlinear load is considered to verify the effectiveness of UPQC for load balancing, power-factor correction, current harmonic mitigation and neutral current compensation. A lagging load is

considered as a linear load, while a diode bridge rectifier drawing constant dc current is considered as the non-linear load. In order to consider the unbalanced load, two-single phase linear load are connected in phase 'b' and 'c' only. The series transformer, ripple filters and APFs are developed using the Power System Blockset toolbox.

Fig.6 shows the response of a three-phase four-wire UPQC with Star-hexagon transformer at the load side. At t=0.05 sec both the shunt and series APF are switched on simultaneously. It is observed from Fig.6 (d) that the supply currents are balanced and sinusoidal while, the load currents are distorted and unbalanced, as shown in Fig.6(e).It is also observer from the Fig.6(g) that source current and source voltage in phase 'a' are exacting in phase, hence shunt APF is compensating for the reactive power along with load balancing and current harmonic mitigation.Fig.6(i) shows that there is a neutral load current because of the unbalanced load, but the star-hexagon transformer is able to mitigate the neutral current as shown in Fig.6(h). Fig. 6(i) shows the neutral current of the star-hexagon transformer, which is exactly opposite to the load neutral current.

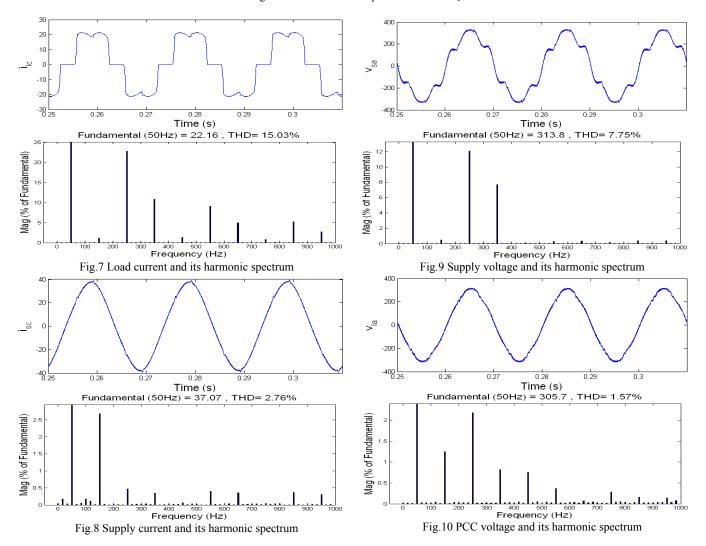

In addition to this, the series APF starts compensating voltage harmonics immediately by injecting out of phase harmonic voltage, making load voltage at load distortion free. The voltage injected by series APF is shown in Fig. 6 (c). Fig. 6(k) shows that during the operation of UPQC dc voltage across the capacitor of back to back VSI is maintained to its reference value. In phase 'c' the THD of load current THD is15.03%, while the THD of source current is 2.76% as shown in Fig.7 and Fig.8, respectively. The harmonic spectrum of load voltage before compensation is shown in Fig.9, while the harmonic spectrum of load voltage after compensation is shown in Fig.10. The load voltage THD is improved form7.75% to 1.57%.

## VI. CONCLUSION

The effectiveness of the proposed UPQC topology has been demonstrated for voltage, harmonic elimination, mitigation of current harmonics, load balancing and power-factor correction. Supply currents and load voltage harmonics levels are maintained below IEEE-519 standards under all conditions. The secondary of the star-hexagon transformer connected near the load, in shunt, effectively compensates the source neutral current. By connecting a star-hexagon transformer on the load side, the rating of the UPQC is reduced due to elimination of a fourth leg compared to three-phase four-leg VSI based In addition to this no extra control is required for the mitigation of neutral current, hence number of current sensors are reduced.

#### **APPENDIX**

The system parameters used are as follows: Supply voltage: 415 V (L-L) RMS, 50Hz. Supply impedance: 1.5mH, 0.  $1\Omega$ . DC link capacitance value:  $3000\mu F$

DC link voltage: 700 V

Fig.6. Performance of Proposed 3P-4W UPQC

#### World Academy of Science, Engineering and Technology International Journal of Electrical and Computer Engineering Vol:5, No:1, 2011

Ripple filter:  $7\Omega$ ,  $5\mu$ F

$K_p = 2, K_i = 2$

Transformer: 250MVA, 58KV/12KV

Linear load: 12KW, 8KVar lagging load in phase 'a' and 'b' Non-Linear load: Three-Phase Rectifier Load R=15 on dc side

#### REFERENCES

- E. W. Gunther and H. Mehta, "A survey of distribution system power quality", IEEE Trans. On Power Delivery, vol.10, No.1, pp.322-329, Jan.1995.

- [2] A. C. Liew, "Excessive neutral current in three-phase fluorescent lighting circuits," IEEE Trans. Ind. Appl., vol.25, no.4, pp.776-782.Jul./Aug. 1989.

- [3] T. M. Gruzs, "A survey of neutral currents in three-phase computer systems, "IEEE Trans. Ind. Appl.,vol.26,no.4,pp.719-725,Jul./Aug.1990.

- [4] IEEE recommended practices and requirements for harmonic control in electric power system, IEEE Std.519, 1992.

- [5] IEEE Recommended Practice for Monitoring Electric Power Quality, IEEE Std. 1159, 1995.

- [6] P. Jayaprakash, B. Singh and D.P. Kothari, Star/Hexagon transformer Based Three-Phase Four-Wire DSTATCOM for Power Quality Improvement," International Journal of Emerging Electric Power System,vol.9,no.8,Article1,Dec.2008.

- [7] J. Praveen , B. P. Muni, S. Venkateshwarlu and H. V. Makthal , " Review of dynamic voltage restorer for power quality Improvement," Proc. IEEE IECON 2004, Nov. 2004, vol. 1, pp. 749-754..

- [8] B. Han, B. Bae, H. Kim and S. Baek, "Combined operation of unified power-quality conditioner with distributed generation," *IEEE Trans. Power Del.*, vol. 21, no. 1, pp. 330–338, Jan. 2006.M. Young, *The Techincal Writers Handbook*. Mill Valley, CA: University Science, 1989

- [9] T. Zhili, L. Xun, C. Jian, K. Yong and D. Shanxu, "A direct control strategy for UPQC in three-phase four-wire system," in *Proc. IEEE Conf. on Power Electron. and Motion Control* 2006,vol.2,pp.1-5.

- [10] V. Khadkikar and A. Chandra, "A Novel Structure for Three-Phase Four-Wire Distribution System Utilizing Unified Power Quality Conditioner (UPQC),"*IEEE Trans. Industry Appl.*,vol.45,pp.1897-1902,2009

- [11] L. Xun, Z. Guorong, D. Shanxu and C. J. Chen, "Control Scheme for Three-Phase Four-Wire UPQC in a Three-Phase Stationary Frame," in *Procd.IEEE/IECON* 2007, pp.1732-1736, 2007.

- [12] A. Ghosh, A. K. Jindal and A. Joshi, "A unified power quality conditioner for voltage regulation of critical load bus," in *Proc. IEEE Power Eng. Society General Meeting*, June 2004, vol.1, pp471-476.

- [13] B. Singh and Venkateswarlu, "A Simplified Control Algorithm for Three-Phase Four-Wire Unified Power Quality Conditioner," Journal of Power Electronics, vol.10, No.1, January 2010.

- [14] G. Chen , Y. Chen and K. M. Smedley , "Three-phase four-leg active power quality conditioner without references calculation," in *Procd. IEEE APEC '04*, vol.1, pp.587-593, 2004.

- [15] V. Kumar, P. Agarwal and H. O. Gupta, "A Simple Control Strategy for Unified Power Quality Conditioner Using Current Source Inverter," in *Procd. IPEC2007*, pp.1219-1223.

- [16] B. Singh, S. Gairola, B. N. Singh, A. Chandar and K. Al-Haddad, "Multipulse AC-DC Converters for improving Power Quality: A Review," *IEEE Trans. On Power Electronics*, vol.23, no.1, pp.260-281, Jan2008.

- [17] B. Singh, S. Gairola, B. N. Singh, A. Chandar and K.Al-Haddad, "Power Quality Improvements in Isolated Twelve-Pulse AC-DC Converters using Delta/Double-Polygon transformer," in Procd. of IEEE PESC, June 2007,pp.2848-2853.

- [18] B. N. Singh, P. Rastgoufard, B. Singh, A. Chandra and K. A. Haddad., "Design, simulation and implementation of the three pole/four pole topologies for active filters," in *Inst. Elect. Engg. Proc. Electr. Power Appl.*, Jul.2004, vol.151, no.4, pp.467-476.

Yash Pal graduated from MMMEC, Gorakhpur, India in 1994 and obtained M.Tech in Control Systems from Regional Engineering College; Kurukshetra, India in 1996.He is currently pursuing Ph.D. and is a Associate Professor at Electrical Engineering Department, NIT, Kurukshetra, India. His research interests include control application to electric power distribution systems, power electronics and power quality.

**A. Swarup** received his Ph.D. in 1993 from IIT Delhi. He is currently working as Professor at Department of Electrical Engineering, NIT, kurukshetra, India. He is a Senior Member of the Institute of Electrical and Electronics Engineers (IEEE). His research interests include robotics and artificial intelligence, system identification, computer networking and control systems.

Bhim Singh(SM'99, F'10) was born in Rahampur, India, in 1956. He received a B.E (Electrical) degree from the University of Roorkee, Roorkee, India, in 1977, and an M.Tech. and Ph.D. from the Indian Institute of Technology (IIT) Delhi, New Delhi, India, in 1979 and 1983, respectively. In 1983, he joined the Department of Electrical engineering at the University of Roorkee, as a lecturer. He became a Reader there in 1988. In December 1990, he joined the Department of Electrical Engineering at the IIT Delhi, as an Assistant Professor. He became an Associate Professor in 1994 and a Professor in 1997. He is a recipient of the JC Bose and the BK Bose awards of the IETE. His fields of interest include power electronics, electrical machines and drives, power quality, FACTs and HVDC system. Prof. Singh is a Fellow of the Indian National Academy of Engineering (INAE), the Institution of Engineers (India) (IE (I)), and the Institution of Electronics and Telecommunication Engineers (IETE). He is also a life Member of the society for Technical Education (ISTE), the System Society of India (SSI), and the National Institute of Quality and Reliability (NIQR) and a Fellow of the Institute of Electrical and Electronics Engineers (IEEE).