# Low Voltage High Gain Linear Class AB CMOS OTA with DC Level Input Stage

Houda Bdiri Gabbouj, Néjib Hassen and Kamel Besbes

Abstract—This paper presents a low-voltage low-power differential linear transconductor with near rail-to-rail input swing. Based on the current-mirror OTA topology, the proposed transconductor combines the Flipped Voltage Follower (FVF) technique to linearize the transconductor behavior that leads to class-AB linear operation and the virtual transistor technique to lower the effective threshold voltages of the transistors which offers an advantage in terms of low supply requirement. Design of the OTA has been discussed. It operates at supply voltages of about  $\pm 0.8 V$ . Simulation results for 0.18  $\mu$ m TSMC CMOS technology show a good input range of 1Vpp with a high DC gain of 81.53dB and a total harmonic distortion of -40dB at 1MHz for an input of 1Vpp. The main aim of this paper is to present and compare new OTA design with high transconductance, which has a potential to be used in low voltage applications.

**Keywords**—Amplifier class AB, current mirror, flipped voltage follower, low voltage.

### I. INTRODUCTION

WITH the scaling down of CMOS technology and the increasing market for portable electronic equipment, the design of high performance low voltage low power analog circuits is becoming increasingly challenging with the persistent trend towards reduced supply voltages.

Thus, for a given technology, reducing the supply voltage can generally degrade the speed of conventional analog circuits. To accomplish these requirements, it is necessary to develop new design technique circuits with low voltage supply without loss of performance [1]-[3]. The operational transconductance amplifier (OTA) is an important bottleneck for various analog circuits and systems. It is widely used as active element in variable gain amplifiers, data converters, interface circuits, continuous time oscillators, switched capacitor filters and sample and hold circuits, etc [1], [4]-[6].

Depending on system needs, OTA circuit with high open loop gain, high slew rate and large bandwidth is highly desired. The high slew rate and bandwidth ensure a small settling time, whereas the high gain improves the settling accuracy [7]-[8]. Unfortunately, all these requirements are difficult to reach with class-A circuits since the maximum

H. Bdiri Gabbouj is with the Faculty of Sciences of Monastir, Tunisia , Boulevard de l'Environnement 5000 Monastir (phone: +21673 500 276; fax: +21673 500 278 ; (e-mail:: houda.bdiri@fsm.rnu.tn).

N. Hassen is with the Faculty of Sciences of Monastir, Tunisia, Boulevard de l'Environnement 5000 Monastir (phone: +21673 500 276; fax: +21673 500 278; (e-mail: nejib.hassen@ fsm.rnu.tn).

K. Besbes is with the Faculty of Sciences of Monastir, Tunisia, Boulevard de l'Environnement 5000 Monastir (phone: +21673 500 276; fax: +21673 500 278; (e-mail: Kamel.besbes@fsm.rnu.tn).

output current is limited by the bias current. Hence, a trade-off between slew rate and power consumption exists [5], [8]. To achieve these desired features, class-AB circuits are often employed. These circuits provide well-controlled quiescent currents, which can be made very low in order to drastically reduce static power dissipation. Traditionally, class-AB transconductors have been designed using two approaches: increasing the tail current of the input pair for large input signals or increasing the current at the active load of the differential input pair. However, a new category of class-AB single stage OTAs which boosts the current both at the differential input transistors and at the active load has been reported. These have been coined as "super class-AB OTAs" [9].

Another limiting factor for OTA performance is the linear output current range which is limited by the supply voltage. So, to provide an extended performance, we are interested in improving dynamic range techniques.

The most common method to achieve extended range is to use a complementary differential amplifier at the input stage [10]-[11]. This method uses a n-type and a p-type differential pairs simultaneously, where the currents of the two input pairs are summed and then sent to the next stage. Complex circuitry is usually required in these circuits to ensure that the sum of the  $g_m s$  of the two input pairs remains constant.

For simplicity and accuracy, it is better to use a single differential pair at the input. In this case, the common mode range of the input pair must be boosted to accept rail to rail inputs.

This paper presents a new approach based on the use of virtual transistor concept to improve input dynamic range. Hence, a new implementation of class-AB transconductance cell using this technique and suited for low voltage operation is obtained. Simulation results of the latter confirm enhancement in linearity input swing and frequency response.

## II. TRANSCONDUCTOR CIRCUIT DESCRIPTION

# A. Basic concept: Super class AB OTA

Given that the function of transconductor is a voltage to current converter, the most critical design requirement is to have high linearity with a good high frequency capability. It is possible to find many researches focusing on this feature. So, different techniques have been proposed to improve the linearity of MOS transconductors such as: source degeneration using resistors or MOS transistors [12]-[13], crossing-coupling of multiple differential pair [14]-[15], class-AB configuration [16]-[17], adaptive biasing [18]-[19],

constant drain-source voltages [20]-[21], pseudo differential stages [22]-[23] and feed-forward technique [4], [24]. In this paper, we will focus on the use of class-AB stages since they may improve considerably the dissipation-speed trade off in analog circuits, as mentioned before.

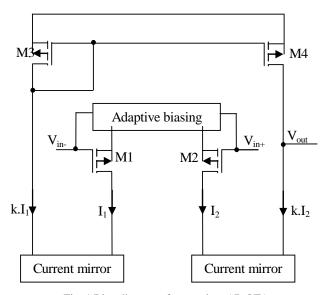

One topology to implement a linear transconductor suitable for low voltage and low power operation is shown in Fig. 1. It is noted "super" class AB OTA in which a double current boosting technique is used: an adaptively biased differential pair [8] and an active load based on current mirrors whose gain is made dependent on their input current [8], [25].

Fig. 1 Bloc diagram of super class AB OTA

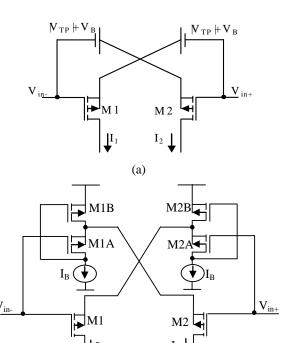

Figure 2(a) shows the chosen adaptively biased input pair as proposed in [5], [8]-[9], [16]. It consists of two matched transistors M1 and M2 cross-coupled by two DC level shifters in order to keep constant sum of source to gate voltages.

The current drain of a conventional differential pair (M1 and M2) operating in saturation mode are given by

$$I_i = \frac{\beta_i}{2} (V_{SGi} - |V_{TP}|)^2 \tag{1}$$

where i=1, 2 denotes transistors Mi,  $\beta_i = \mu_n C_{ox}(W/L)_{M_i}$  is the transconductance factor of transistors Mi and  $|V_{TP}|$  is the threshold voltage of PMOS transistor.

Assuming  $\beta_1 = \beta_2 = \beta$ , the differential output current is defined as

$$I_d = I_1 - I_2 = \frac{\beta}{2} (V_{SG1} + V_{SG2} - 2 | V_{TP} |) (V_{SG1} - V_{SG2})$$

(2)

From the latter, to have a linear current  $I_d$ , the term  $V_{SG1} + V_{SG2} - 2|V_{TP}|$  should be kept constant. An efficient way consists in integrating two floating DC voltage sources with values  $V_B + |V_{TP}|$  as depicted in Fig. 2(a).

Fig. 2. Class AB input stage using cross coupled differential pair (a) diagram (b) implementation using FVF

From the loop around the input transistors, the relationship between  $V_{SG1}$  and  $V_{SG2}$  as a function of  $V_{in+}$  and  $V_{in-}$  are given by

$$V_{SG1} = (V_{in+} - V_{in-}) + (V_B + |V_{TP}|)$$

$$V_{SG2} = (V_{in-} - V_{in+}) + (V_B + |V_{TP}|)$$

(3)

The sum and difference of these two relations gives

$$V_{SG1} + V_{SG2} = 2(V_B + |V_{TP}|) \tag{4}$$

$$V_{SG1} - V_{SG2} = 2(V_{in+} - V_{in-})$$

(5)

Substituting expression (4) and (5) in expression (2), the output differential current, which shows the well by  $V_B$ , is written as

$$I_d = 2\beta V_B (V_{in+} - V_{in-}) = g_m V_{id}$$

(6)

The linear input signal range is bounded by

$$\left| V_{id} \right| < V_B \tag{7}$$

The linear output range is bounded by

$$|I_d| < 2\beta V_B^2 \tag{8}$$

Figure 2(b) shows an efficient implementation of very low impedance voltage source which offers more accurate voltage level shift than a conventional source follower buffer. Each level shifter is built by "Flipped Voltage Follower" FVF cell. FVF cells are composed by two transistors (M1A, M2A and M1B, M2B) and a current source I<sub>B</sub>. Assuming matched transistors M1, M2, M1A and M1B, the source-gate voltage of M1A respectively M2A is defined as

$$V_{SG,1A,2A} = V_{SDsat,1A,2A} + |V_{TP}| = V_B + |V_{TP}|$$

(9)

in which the DC level shifter voltage,  $V_{\text{B}}$ , is written as

$$V_B = \sqrt{\frac{2I_B}{\beta_{1A,2A}}} \tag{10}$$

By replacing this expression in (6), the differential current  $I_d$ , which shows the well controlled bias current  $I_B$ , is derived as

$$I_d = I_1 - I_2 = 2\beta \sqrt{\frac{2I_B}{\beta_{1A,2A}}} V_{id}$$

(11)

Obviously,  $I_d$  is linearly proportional to differential input voltage  $V_{id}$  and the transconductance  $g_m$  is expressed as

$$g_m = 2\beta \sqrt{\frac{2I_B}{\beta_{1A,2A}}} \tag{12}$$

This class-AB input stage using cross coupled differential pair can be operated with a minimum supply voltage of

$$V_{DD,\min} = \left| V_{TP} \right| + V_{SDsat,1} + V_{SDsat,2B} \tag{13}$$

where V<sub>SD,sat</sub> denotes source-drain saturation voltage.

This implementation features very low output impedance, large current sourcing capability, low voltage operation and low standby current consumption [16], [26].

However and especially for low voltage design, the most critical parameter of this transconductor is a limited common mode input voltage range as given by equation (14)

$$V_{SS} + V_{DSsat,mirror} - \left| V_{TP} \right| < V_{CMR} < V_{DD} - V_{SDsat,1} - V_{SDsat,2B} - \left| V_{TP} \right|$$

$$\tag{14}$$

According to this relationship, a dissymmetric behavior of the input dynamic range is observed. The input dynamic range is significantly important in the negative part that in the positive one. In the following part, we will present an efficient approach to shift the input dynamic range with a symmetric behavior.

### B. DC level input stage

In order to have a transconductor with higher linearity and wider input voltage differential mode range, we will try, in this section, to extend the linear region of the input stage

As shown in equation (14), the dynamic range is limited by the threshold voltage and the drain-source saturation voltage of the MOS transistor for operation in the strong inversion region. So, an efficient way to make the dynamic range symmetrical is to lower the threshold voltage. It is possible to find many researches focusing on this feature and considering low voltage applications or low threshold voltage transistor. Low voltage strong inversion operation can be achieved using bulk driven transistors [27], [28], floating gate transistors [29], [30] and dynamically biased stages [31]. Unfortunately, these approaches may introduce a loss of performance (g<sub>m</sub> and g<sub>0</sub> will be degraded).

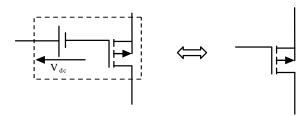

To overcome this limitation, an approach illustrated in Fig. (3) consists in adding a DC level shifter  $V_{\rm dc}$ , in series with the gate of the PMOS transistor. This voltage introduces a translation of the operating point of the transistor in the amplification zone which leads to the reduction of the

threshold voltage. The effective threshold voltage will be given by

$$\left| V_T' \right| = \left| V_{TP} \right| - V_{dc} \tag{15}$$

With this approach and biased at the same drain current level,  $g_m$  and  $g_0$  of the transistor will be conserved.

Fig. 3 "Virtual" transistor concept PMOS version

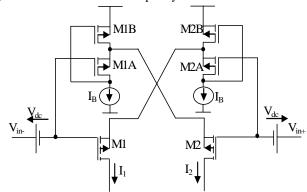

Figure 4 shows the modified version of Fig. 2 which uses "virtual" transistor concept. In this case, the common mode range will be extended by  $V_{\text{dc}}$  amount, as given by

$$V_{SS}+V_{DSsanirror}|V_{TP}+V_{dc}< V_{CMR} \cdot V_{DD}-V_{SDsat}-V_{SDsab}-|V_{TP}+V_{dc}|$$

(16)

The voltage  $V_{\text{dc}}$  is chosen to have simultaneously a symmetrical and maximum input dynamic.

Fig. 4 Class AB input stage with extended input range

The chosen DC level shifter implementation is the conventional NMOS source follower, as shown in Fig. 5.

Fig. 5 DC level shifter implementation

If a high impedance current source is provided to the source follower,  $V_{dc}$  is considered to be constant. It is given by

$$V_{dc} = \sqrt{\frac{2I_D}{\beta}} + V_{TN} \tag{17}$$

### C.. Full circuit implementation

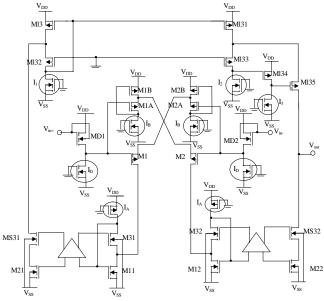

As summarized in Fig. 6, a new high performance CMOS OTA topology is proposed by replacing the conventional class AB input stage using cross coupled differential pair with the modified input stage described above.

Fig. 6 Proposed transconductor implementation

The proposed OTA, whose synoptic schematic is seen in Fig.1, incorporates some important modifications. We have used two types of current mirror high performance with low operating voltage [32]-[33]. These two structures have a wide bandwidth and high output impedance to have a very high GBW the OTA. The PMOS current mirror connected to  $V_{\rm DD}$  is the one proposed in [32]. Due to the input feedback, which consists of the transistor Ml32, the current source  $I_1$  and the voltage source  $V^{\rm B}$ , it reaches low input impedance given by

$$R_{in} = \frac{1}{g_{m,l32}g_{m,l3}r_{o,l32}}$$

(18)

and very high output impedance given by

$$R_{out} = g_{m,l34} r_{o,l34} g_{m,l35} r_{o,l35} g_{m,l35} r_{o,l35} r_{o,l35} r_{o,l31}$$

(19)

The NMOS current mirrors connected to  $V_{SS}$  are of type flipped voltage follower (FVF) current mirror with regulated cascode output based on full balanced pseudo amplifier's A [33]. Its input impedance is further reduced by the input shunt feedback loop. It's given by

$$R_{in} = \frac{1}{A g_{m1} g_{m1C} r_{o1C}}$$

(20)

This version allows very high output impedance by the amplifier's gain A. Its value is

$$R_{out} = Ar_{o2}g_{m2C}r_{o2C} \tag{21}$$

### III. SIMULATION RESULTS

The proposed transconductor is simulated using BSIM3v3 Spice models for a TSMC 0.18 $\mu$ m CMOS technology with deep-Nwell process available from MOSIS [34]. Nominal PMOS- and NMOS- transistor threshold voltages in this technology are 0.51V and 0.5V, respectively. This circuit is operated at  $\pm$  0.8V supply voltage with a capacitive load of 10pF. The proposed circuit, with and without DC level input stage designated respectively OTA3, OTA2, is validated through the one presented in [8] denoted OTA1. Transistor sizes and values of biasing currents are shown in Table I.

TABLE I

TRANSISTOR SIZES AND BIAS CONDITION FOR ALL CIRCUITS OF OTA

| Transistor |              | Size         |      |

|------------|--------------|--------------|------|

|            | OTA3         | OTA2         | OTA1 |

| M1, 2      |              | 5μm/0.18μm   |      |

| M2A, 2B    |              | 30µm/0.18µm  |      |

| M1A, 1B    |              | 3.5µm/0.18µm |      |

| MD1, D2    | 23µm/0.18µm  | -            | -    |

| M11, 12,   |              | 30µm/0.18µm  |      |

| 21, 22,    |              |              |      |

| MS31,S32   |              | 90μm/0.18μm  |      |

| M31, 32    | 3μm/0.1      | 30µm0.18µm   |      |

| MI3, I31   | 50μm/0.1     | 2μm0.18μm    |      |

| MI32, 133  | 3µm/0.1      | -            |      |

| Ml34       | 5μm/0.1      | -            |      |

| Ml35       | 40μm/0.1     | -            |      |

| $I_{1, 2}$ | 5.12μ        | -            |      |

| $I_3$      | 10μ <i>A</i> | -            |      |

| $I_{A,B}$  |              |              |      |

| $I_D$      | 8.10µA       | -            | -    |

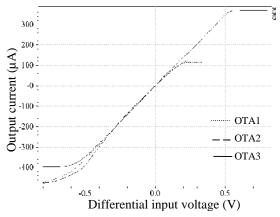

Figure 7 shows the DC characteristic for all circuits of OTA. The latter shows the differential output current, for a DC sweep of differential input voltage from -0.8V to +0.8V. It proves the effectiveness of the virtual transistor concept in improving the dynamic range of the transconductor with nearly the same slope. The DC transconductance  $(g_m)$  is approximately  $700\mu S$ . Differential output current shows a symmetrical and linear behavior over a differential input voltage range of  $\pm 0.5 V$  for OTA3 while it is about of  $\pm 0.2 V$  for both OTA2 and OTA1.

Figure 8 shows the linearity error against differential input voltage curve for all circuits of OTA. The error is defined as:

$$\varepsilon(\%) = \frac{I_{out} - I_{out}(0) - g_m(0)V_{id}}{g_m(0)V_{id}} \times 100$$

(22)

where  $I_{out}(0)$  and  $g_m(0)$  denote respectively the differential output current and the transconductance value for  $V_{id}$ =0.  $I_{out}(0)$  must be subtracted from  $I_{out}$  to remove the contribution of any dc offset to  $I_{out}$ . For the proposed circuit (OTA3), the linearity error is less than 0.2% for the whole dynamic range.

Fig. 8 Linearity error of the transconductor OTA1, 2, 3

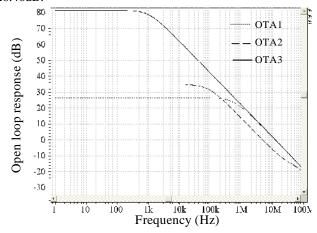

Figure 9 shows the open loop frequency response for all circuits of OTA. A high open loop gain of 81.53dB with a large GBW of 12.45MHz is reached by OTA3. For OTA2, we note a low open loop gain closed to 34.86dB. The least one is attained by the basic transconductor (OTA1), it is about 26.46dB.

Fig. 9 Open loop frequency response of the OTA1, 2, 3

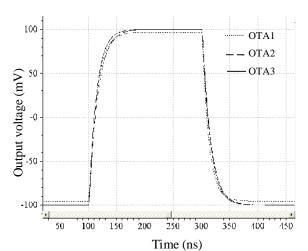

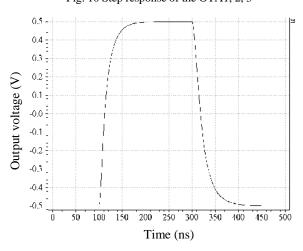

The simulated rise and fall step response of all circuits of OTA for 0.2Vpp and 1Vpp input differential voltage is, respectively, shown in Fig. 10 and Fig. 11.

Fig. 10 Step response of the OTA1, 2, 3

Fig. 11 Step response of the OTA 3

TABLE II SIMULATION AND BIAS COMPARISON RESULTS

| Parameter                                            | OTA3     | OTA2   | OTA1   |               |        |  |

|------------------------------------------------------|----------|--------|--------|---------------|--------|--|

|                                                      | 1        |        | _      |               |        |  |

| Capacitive load                                      |          |        |        | 10pF<br>±0.8V |        |  |

| Supply voltage                                       |          |        |        | ±0.6 V        |        |  |

| Positive slew rate (V/µs)                            | 0.2Vpp   |        | 5.37   | 4.63          | 4.93   |  |

|                                                      | 1Vpp     |        | 24.09  | -             | -      |  |

| Negative                                             | 0.2Vpp   |        | 5.31   | 5.10          | 6.25   |  |

| slew rate<br>(V/μs)                                  | 1Vpp     |        | 18.71  | -             | -      |  |

|                                                      |          |        | 61.33  | 69.69         | 62.53  |  |

| 1% settling time (ns)                                | positive | 0.2Vpp | 01.33  | 09.09         | 02.33  |  |

|                                                      | 1        | 1Vpp   | 75.53  | -             | -      |  |

|                                                      | negative | 0.2Vpp | 64.63  | 68.63         | 57.03  |  |

|                                                      | negative | 1Vpp   | 83.43  | -             | -      |  |

| THD (dB) @                                           | 0.2Vpp   |        | -46.35 | -39.33        | -42.81 |  |

| 1MHz                                                 | 1Vpp     |        | -39.86 | -             | -      |  |

|                                                      | 23.07    | 15.67  | 14.112 |               |        |  |

| Noise level nV/ $\sqrt{Hz}$ @ 1MHz $\frac{25.07}{8}$ |          |        |        |               |        |  |

| CMRR (dB)                                            | 67.51    | 72.98  | 41.43  |               |        |  |

| PSRR+ (dc) (dB)                                      |          |        | 65.59  | 70.81         | 32.88  |  |

| PSRR- (dc) (dI                                       | 68.16    | 47.92  | 33.43  |               |        |  |

| Static power consumption (mW)                        |          |        | 0.325  | 0.225         | 0.191  |  |

| Open loop voltage gain(dB)                           |          |        | 81.53  | 34.86         | 26.46  |  |

| GBW (MHz)                                            | 12.45    | 4.74   | 12.05  |               |        |  |

| Phase margin (degrees)                               |          |        | 86.09  | 95.3          | 90.21  |  |

Table II summarizes all the simulated results of the proposed OTA (OTA3, 2) and compares them with the basic one (OTA1).In order to evaluate our work towards other works, the defined Figure Of Merit, which weighs the tradeoff between

the transconductance value, linearity performance, speed of the circuit, input swing range and power consumption into account, is expressed as follows:

$$FOM = 10\log(\frac{g_m \cdot V_{id} \cdot |THD_{dB}| \cdot f_0}{Power})$$

(23)

This comparison is given in Table III.

TABLE III

PERFORMANCE COMPARISON WITH PREVIOUSLY REPORTED WORKS

| Performance design      | OTA3                    | OTA [5]       | OTA [8]            | OTA [9] | OTA [16] | OTA [17] | OTA [25] | OTA [35] |

|-------------------------|-------------------------|---------------|--------------------|---------|----------|----------|----------|----------|

| Technology CMOS (µm)    | TSMC 0.18               | AMI 0.5       | AMI 0.5            | 0.5     | AMS 0.8  | 0.8      | AMS      | 0.5      |

|                         |                         |               |                    |         |          |          | 0.35     |          |

| Supply voltage (V)      | $\pm 0.8$               | $\pm 1$       | ±1                 | ±1      | +1.5     | +2       | ±0.75    | 1.8      |

| Load (pF)               | 10                      | 80            | 80                 | 80      | -        | -        | 15       | -        |

| Transconductance value  | 700                     | -             | -                  | -       | 155      | 207      | -        | 80       |

| (μS)                    |                         |               |                    |         |          |          |          |          |

| Input swing range (Vpp) | 1                       | 0.9           | 0.9                | 0.9     | 0.6      | 0.6      | -        | 2        |

| DC gain (dB)            | 81.53                   | 43            | 37                 | -       | -        | 51.37    | 78       | -        |

| GBW (MHz)               | 12.45                   | 0.725         | 3.27               | 0.900   | -        | -        | 8.9      | -        |

| Phase margin (degrees)  | 86.09                   | 89.5          | 56                 |         | -        | -        | 81       | -        |

| PSRR+ (dB)              | 65.59                   | 55            | 41                 | -       | -        | -        |          | -        |

| PSRR- (dB)              | 68.16                   | 58            | 52                 | -       | -        | -        |          | -        |

| CMRR (dB)               | 67.51                   | 68            | 85                 | -       | -        | -        | 126      | -        |

| THD (dB)                | -39.86                  | -56           | -37                | -56.47  | -37.33   | -40      | -        | -67      |

| @ voltage peak -peak    | 1Vpp                    | 0.9Vpp        | 0.9Vpp             | 0.9Vpp  | 0.2Vpp   | -        |          | 1Vpp     |

| @ frequency             | 1MHz                    | 100kHz,       | 100kHz,            | 100kHz  | 5MHz     | 10.7MHz  |          | 1MHz     |

| Figure of merit         | 83.26                   | 82.36         | 76.76              | 83.54   | 84.33    | 84.60    |          | 86.96    |

| Output Noise Density    | -152,8                  | 230           | -145.5             | -       | -        | -        | -        | -        |

|                         | $dBV_{rms} / \sqrt{Hz}$ | $\mu V_{rms}$ | $dBV_{rms}$        |         |          |          |          |          |

|                         | GE THIS VIIE            | @1MHz         | $\sqrt{\text{Hz}}$ |         |          |          |          |          |

| Power consumption (mW)  | 0.325                   | 0.120         | 0.220              | 0.120   | 0.042    | 0.46     | 0.169    | 0.360    |

### IV. CONCLUSION

The resulting topology achieves a good input range of 1Vpp with a high DC gain of 81.53dB in ±0.8V supply voltage. The GBW is 12.45MHz and the total harmonic distortion THD is about -40dB for 1Vpp input signal at 1MHz. Besides, the OTA shows high slew rate and low settling time.

# REFERENCES

- [1] Tien-Yu Lo and Chung-Chih Hung, "A wide tuning range Gm-C continuous- time analog filter," *IEEE Trans. Circuits Syst. I*, vol. 54, no. 4, pp.713-722, 2007.

- [2] J. Ramirez-Angulo, R.G. Carvajal, A. Torralba, J. Galan, A.P. Vega-Leal and J. Tombs, "The Flipped Voltage Follower: A useful cell for low voltage low power circuit design," *IEEE Int, Symp. on Circuits and Systems*, vol.3, pp. 615-618, 2002.

- [3] Markus Helfenstein, Qiuting Huang and Geoge S. Moschytz, "90 dB, 90 MHz, 30 mW CMOS OTA for a high capacitive load," *International Journal of Circuit Theory and Application, Int. J. Circ. Theor. Appl.*, vol. 27, no. 5, pp. 473-483, 1999.

- 4] Stanislaw Szczepanski, Bogdan Pankiewicz and Slawomir Koziel "Programmable feedforward linearized CMOS OTA for fully differential continuous-time filter design," *International Journal of Circuit Theory and Design, Int. J. Circ. Theor. Appl.* 2009.

- [5] Antonio J. Lopez-Martin, Sushmita Baswa, Jaime Ramirez –Angulo and Ramon Gonzalez Carvajal, "Low voltage super class AB CMOS OTA cells with very high slew rate and power efficiency," *IEEE Journal of Solid-State Circuits*; vol. 40, no. 5, pp.1068-1077, 2005.

- [6] Antonio J. Lopez-Martin, Jaime Ramirez Angulo, Chandrika Durbha and Ramon Gonzalez Carvajal, "A CMOS Transconductor with multidecade tuning using balanced current scaling in moderate inversion," *IEEE Journal of Solid-State Circuits*, vol. 40, no. 5, pp.1078-1083, 2005.

- [7] Renato Rimolo-Donadio, Alexander Mora-Sanchez and Dietmar Schroeder, "High slew rate configurable class AB fully differential operational transconductance amplifier for switched capacitor circuit applications," Workshop on Circuits, Systems and Signal Processing PRORISC 2006 Veldhoven (The Netherlands).

- [8] Juan A. Galan, Antonio J. Lopez-Martin, Ramon Gonzalez Carvajal, Jaime Ramirez-Angulo and Carlos Rubia-Marcos, "Super class AB OTAs with adaptive biasing and dynamic output current scaling," *IEEE Transactions on Circuits and Systems-I: regular papers*, vol. 54, no. 3pp.449-457, 2007.

- [9] S. Baswa, Antonio J. Lopez-Martin, Jaime Ramirez-Angulo and Ramon Gonzalez Carvajal, "Low voltage micro-power super class AB CMOS OTA," *Electronics letters*, vol. 40, no. 4, pp.216-217, 2004.

- [10] F. Palma and S. Durante, "Gm-Extraction for rail-to-rail input stage linearization," *International Journal of Circuit Theory and Design, Int. J. Circ. Theor. Appl.*, vol. 33, no. 6, pp.541-552, 2005.

- [11] Carrillo JM, Duque-Carrillo JF, Torelli G, Ausin JL, "Constant-gm constant-slew-rate high-bandwidth low-voltage rail-to-rail CMOS input stage for VLSI cell libraries," *IEEE Journal of Solid-State Circuits*, vol. 38, no. 8, pp.1364–1372, 2003.

- [12] Monsuro P, Pennisi S, Scotti G, Trifeletti A, "Linearization technique for source-degenerated CMOS differential transconductors," *IEEE Transactions on Circuits and Systems II*, vol. 54, no. 10, pp.848–852, 2007.

- [13] Ergun B. S. and Kuntman H, "On the design of new CMOS DO-OTA topologies providing high output impedance and extended linearized range," *Istanbul University, Journal of Electrical and Electronics Engineering*, vol. 5, no. 2, pp.1449-1461, 2005.

- [14] Chen J., Sanchez-Sinencio E., Fellow IEEE, and Silva-Martinez J., "Frequency-Dependent Harmonic-Distortion Analysis of a Linearized Cross-Coupled CMOS OTA and its Application to OTA-C Filters," *IEEE Transaction on Circuit and Systems*, vol. 53, no. 3, pp.499-510, 2006.

- [15] Manuel Carrasco-Robles and Luis Serrano, "Obtaining maximally flat transconductances with any number of multiple coupled differential pairs," *International Journal of Circuit Theory and Application, Int. J. Circ. Theor. Appl.* 2009.

- [16] M. Laguna, C. De la Cruz-Blas, A. Torralba, R.G. Carvajal, A. Lopez-Martin and A. Carlosena, "A novel low voltage low power class AB linear transconductor," *IEEE International Symposium on Circuits and Systems ISCAS*, vol.1, pp. 725-728, 2004.

- [17] J.A. Galan, R. G. Carvajal, F. Munog, A. Torralba and J. Ramirez-Angulo, "Low power low voltage class AB linear OTA for HF filters with a large tuning range," *IEEE Transactions on Circuits and Systems*, vol. 2, pp. 9-12, 2002.

- [18] M. G. Degrauwe, J.Rijmenants and E. A. Vittoz, "Adaptive biasing CMOS amplifiers," *IEEE Journal of Solid State Circuits*, vol. 17, no. 3, pp. 522-528, 1982.

- [19] S. Sengupta, "Adaptively biased linear transconductor," *IEEE Transactions on Circuits and Systems*, vol. 52, no. 11, pp. 2369-2375, 2005.

- [20] Ayman A. Fayed and Mohammed Ismail , "A Low-Voltage, Highly Linear Voltage-Controlled Transconductor," *IEEE Transactions on Circuits and Systems-II: Express briefs*, vol. 52, no. 12, pp. 831-835, 2005.

- [21] Ko-Chi Kuo and Hsing-Hui Wu "A Low-Voltage, Highly Linear, and Tunable Triode Transconductor," *Electron Devices and Solid-State Circuits EDSSC*, pp. 365-368; 2007.

- [22] A. Gharbiya and M. Syrzycki, "Highly linear, tunable, pseudo differential transconductor circuit for the design of Gm-C filters," *IEEE Canadian Conference on Electrical and Computer Engineering CCECE*; vol.1, pp. 521-526, 2002.

- [23] B. Calvo, S. Celma, J. Ramirez-Angulo and M.T. Sanz, "Low-voltage pseudo-differential transconductor with improved tunability-linearity trade-off," *Electronics Letters*, vol.42, no. 5, pp.862-863, 2006.

- 24] SzczepanskiS. and Koziel S., "Phase compensation scheme for feedforward linearized CMOS operational transconductance amplifier," *Bulletin of the Polish Academy of Sciences*, vol. 52, no. 2, pp. 141-148, 2004.

- [25] Giuseppe Ferri, Vincenzo Stornelli, and Angelo Celeste, "Integrated Rail-to-Rail Low-Voltage Low-Power Enhanced DC-Gain Fully Differential Operational Transconductance Amplifier," ETRI Journal, vol. 29, no. 6, pp. 785- 793, December 2007.

- [26] R. G. Carvajal, J. Ramirez Angulo, A. J. López-Martín, A. Torralba, J. Galán, A. Carlosena, F. Muñoz, "The Flipped Voltage Follower: A useful cell for low-voltage low-power circuit design," *IEEE Trans. Circuits Syst. I*, vol. 52, no. 7, pp.1276-1291, 2005.

- [27] Pietro Monsurr`o, Salvatore Pennisi, Giuseppe Scotti and Alessandro Trifiletti, "0.9-V CMOS cascade amplifier with body-driven gain boosting," *International Journal of Circuit Theory and Design, Int. J. Circ. Theor. Appl.* 2009.

- [28] Xuguang Zhang and Ezz. I. El-Masry "A low voltage body driven CMOS transconductor," Midwest Symposium Circuits and Systems MWSCAS; vol.1, pp.328-331, 2002.

- [29] J. Ramirez-Angulo; S.C. Choi; G. Gonzalez-Altamirano "Low-voltage circuits building blocks using multiple-input floating-gate transistors," *IEEE Transactions on Circuits and Systems I: Fundamental Theory and Applications*; vol. 42, no. 11, pp. 971 –974, 1995.

- [30] Chong-Gun Yu; R. L. Geiger, "Very low voltage operational amplifiers using floating gate MOS Transistor," *IEEE International Symposium on Circuits and Systems*, pp. 1152 –1155, 1993.

- [31] G. Giustolisi; G. Palmisano; T. Segreto. "1.2-V CMOS op-amp with a dynamically biased output stage," *IEEE Journal of Solid-State Circuits*, vol. 35, no. 4, pp. 632 –636, 2000.

- [32] A.Torralba, R.G. Carvajal, J. Ramirez-Angulo and F. Munoz "Output stage for low supply voltage, high performance CMOS current mirrors," *Electronics letters*, vol. 38, no. 24, pp.1528-1529, 2002.

- [33] Néjib Hassen, Houda Bdiri Gabbouj and Kamel Besbes, "Low voltage high performance current mirros: application to linear voltage to current converter," *International Journal of Circuit Theory and Design, Int. J. Circ. Theor. Appl.* 2009.

- [34] The MOSIS service, "Wafer electrical test dada and spice model parameters," http://www.mosis.org/test/

- [35] Juan Antonio Gómez Galán, Manuel Pedro Carrasco, Melita Pennisi, Antonio Lopez Martin, Ramon González Carvajal, and Jaime Ramírez-Angulo, "Low-Voltage Tunable Pseudo-Differential Transconductor with High Linearity," ETRI Journal, vol. 31, no. 5, pp. 576-584, October 2009.