# Implemented 5-bit 125-MS/s Successive Approximation Register ADC on FPGA

S. Heydarzadeh, A. Kadivarian, P. Torkzadeh

*Abstract*—Implemented 5-bit 125-MS/s successive approximation register (SAR) analog to digital converter (ADC) on FPGA is presented in this paper.The design and modeling of a high performance SAR analog to digital converter are based on monotonic capacitor switching procedure algorithm .Spartan 3 FPGA is chosen for implementing SAR analog to digital converter algorithm. SAR VHDL program writes in Xilinx and modelsim uses for showing results.

*Keywords*—Analog to digital converter, Successive approximation, Capacitor switching algorithm, FPGA

I

#### INTRODUCTION

UCCESSIVE approximation register (SAR) analog-to S digital converters (ADCs) require several comparison cycles to complete one conversion, and therefore have limited operational speed. SAR architectures are extensively used in low-power and low-speed (below several MS/s) applications. In recent years, with the feature sizes of CMOS devices scaled down, SAR ADCs have achieved several tens of MS/s to low GS/s sampling rates with 5-bit to 10-bit resolutions [1],[2]. Successive approximation register (SAR) converters offer the combination of resolution and speed unmatched by deltasigma, pipeline or flash type ADCs. SAR's have no latency, and can be multiplexed. Furthermore, the power consumption is relatively low. These features make SAR converters suitable for data acquisition and fiber-optic applications [3]. The main reason, which limited SAR resolution and speed, is comparison cycles to complete one conversion. Monotonic capacitor switching procedure algorithm as compared to conventional algorithm uses less comparsion cycles. This paper proposes implementing a capacitor switching procedure algorithm on FPGA to show industrial applications of this method.

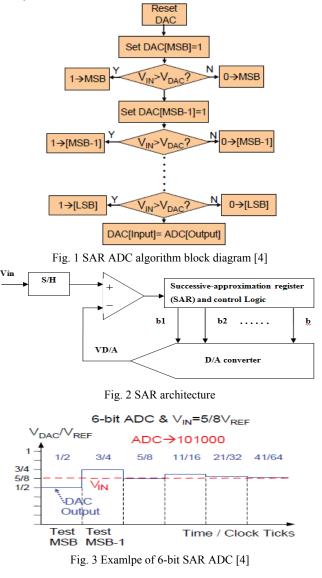

### II. CONVENTIONAL SAR ARCHITECTURE

A successive approximation ADC works by using a digital to analog converter (DAC) and comparator to perform a binary search to find the input voltage. A sample and hold circuit (S&H) is used to sample the analog input voltage and hold the sampled value whilst the binary search is performed. The binary search starts with the most significant bit (MSB) and works towards the least significant bit (LSB). For a 8-bit output resolution, 8 comparsion cycles are needed in binary search ,taking a least 8 clock cycles.

Siavash Heydarzadeh is with Sience and Research Branch Islamic Azad University, Iran e-mail:siavash136725@yahoo.com

The sample and hold circuit samples the analog input on a rising edge of sample signal. The comparator output is a logic 1 if the sampled analog voltage is greater than the output of DAC, 0 otherwise. Figure 1 shows SAR algorithm based on binary search over DAC output.

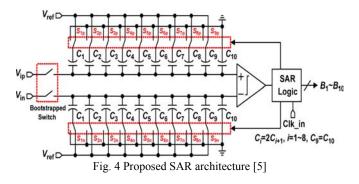

III. PROPOSED SAR ARCHITECTURE

Figure 4 shows the proposed SAR ADC, where the proposed Switching procedure can be either upward or downward.

For fast reference settling, discharging through n-type transistors, downward switching was selected in this ADC. The proposed ADC samples the input signal on the top plates via bootstrapped switches, which increases the settling speed and input bandwidth. At the same time, the bottom plates of the capacitors are reset to Vref . Next, after the ADC turns off the bootstrapped switches, the comparator directly performs the first comparison without switching any capacitor. According to the comparator output, the largest capacitor C1 on the higher voltage potential side is switched to ground and the other one (on the lower side) remains unchanged. The ADC repeats the procedure until the LSB is decided. For each bit cycle, there is only one capacitor switch, which reduces both charge transfer in the capacitive DAC network and the transitions of the control circuit and switch buffer, resulting in samaller power dissipation. This proposed SAR ADC uses less compaton cycles as compared to conventional SAR [5].

## IV. IMPLEMENTED SPECIFICATIONS FPGA specification: Family : Spartan 3 Device : XC3S50 Package: PQ208

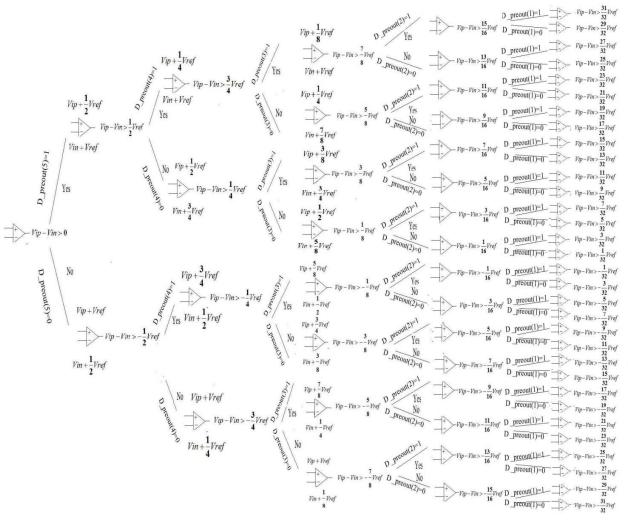

Fig. 5 SAR algorithm implemented on FPGA

Figure 5 displays the SAR algorithm (based on proposed SAR acrchitecture as showen in Fig.4) witch implemented on FPGA.

Digital sinusodial voltage has been created with lookuptable for input voltage in testbench.Figure 6 shows SAR ADC block diagram witch implemented on FPGA.

Fig. 6 Implemented SAR ADC Block diagram

For Simplicity in simulation, sinusodial input voltage shifts to achieve positive input amplitude as figure 7 shows. Therefore top side of SAR algorithm (Top side in Fig 5) is needed to implement.

Fig. 7 a)Sinusodial input voltage without shift b)Sinusodial input voltage with shift

#### V. SIMULATION RESULTS

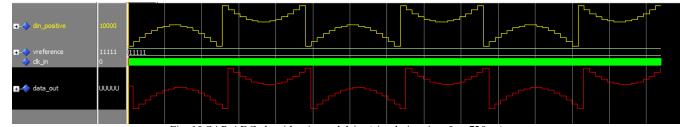

SAR ADC VHDL program synthesis in Xilinx and Simulation results represent in figure 8 to 10. Modelsim and Xilinx Isim used to show final results.

#### VI. CONCLUSION

The proposed SAR analog to digital converter (5-bit and 125MS/s) has been successfully simulated. Monotonic capacitor switching procedure algorithm implemented on spartan3 FPGA.Simulation results in Xilinx Isim and modelsim express that, this algorithm Can be used in industry.The reviewer can develop proposed algorithm (Fig 5) to achieve high resolution and, with decreasing clock cycles high speed is obtainable.

#### ACKNOWLEDGMENT

The authors thank to M, Jafaripanah and H. Darvish for their help.

#### References

- C. C. Liu, S. J. Chang, G. Y. Huang, and Y. Z. Lin, "A 0.92mW10-bit 50-MS/s SAR ADC in 0.13 µm CMOS process," in IEEE Symp. VLSI Circuits Dig., Jun. 2009, pp. 236–237.

- [2] V. Giannini, P. Nuzzo, V. Chironi, A. Baschirotto, G. Van der Plas, and J. Craninckx, "An 820 μW 9 b 40 MS/s noise-tolerant dynamic-SAR ADC in 90 nm digital CMOS," in IEEE ISSCC Dig. Tech. Papers, Feb. 2008, pp. 238–239.

- [3] J.Gan,S.Yan,J. Abraham, "Design and Modeling of a 16-bit 1.5MSPS Successive Approximation ADC with Non-binary Capacitor Array," GLSVLSI '03, April 28-29, 2003, Washington, DC, USA.

- [4] EECS 247 Lecture 18: Data Converters- Track & Hold- ADC Design 2009.

- [5] Ch-Ch.Liu, S-J. Chang,G-Y. Huang, Y-Z Lin, "A 10-bit 50-MS/s SAR ADC With a Monotonic Capacitor Switching Procedure," IEEE JOURNAL OF SOLID-STATE CIRCUITS, VOL. 45, NO. 4, APRIL 2010.

- [6] M. Yoshioka, et Al. "A 10b 50MS/s 820 μW SAR ADC withOn-Chip Digital Calibration," IEEE ISSCC Dig. Tech. Papers,pp. 384-385, Feb. 2010.

- [7] F. Kuttner, "A 1.2-V 10-b 20-Msample/s nonbinary successive approximation ADC in 0.13-μm CMOS," in IEEE ISSCC Dig. Tech. Papers, Feb. 2002, pp. 176–177.

- [8] T. Kugelstadt, "The Operation of the SAR-ADC Based on Charge Redistribution", Texas Instruments Analog Applications Journal, Feb. 2000, pp. 10-12.

- [9] Gilbert Promitzer, "12 Bit Low Power Fully Differential Switched Capacitor Non-Calibrating Successive Approximation ADC with 1MS/s," IEEE J. Solid-State Circuits, vol. 36, no. 7, pp. 1138-1143, July. 2001.

#### World Academy of Science, Engineering and Technology International Journal of Electronics and Communication Engineering Vol:6, No:9, 2012

|                          |         |      |        |       |        |                     |       |      |    |    |    |              |      |       |      |      |    |     |      |     |       |     |    |      |     |     |    |      |      |      |      |      |    |      |      |    |       |       |      |      |       |      |      |       | 3     | 59.9                | )5 ns |

|--------------------------|---------|------|--------|-------|--------|---------------------|-------|------|----|----|----|--------------|------|-------|------|------|----|-----|------|-----|-------|-----|----|------|-----|-----|----|------|------|------|------|------|----|------|------|----|-------|-------|------|------|-------|------|------|-------|-------|---------------------|-------|

| Name                     | Value   | 0 ns |        |       |        |                     | 5     | 0 ns |    |    |    |              |      | 100   | ns   |      |    |     |      | l   | 150 n | S   |    |      |     |     | 20 | 0 ns |      |      |      |      |    | 25   | 0 ns |    |       |       |      |      | 300 i | ns   |      |       |       |                     | 350 n |

| ▶ 💐 din_positive[4:0]    | 19      | 16   | 19 /2  | 2)(2  | 5 / 27 | 7 29                | ) (80 | )(   | 31 | 30 | 29 | ) <u>/</u> 2 | 7)(2 | 5/2   | 2)(  | 19   | 16 | 13  | (10) | 7   | 5     | 3   | 2  | X    | 1   | 2 ( | 3  | X5   | X    | 7)(1 | IO X | 13   | 16 | (19  | 22   | 25 | 27    | 29    | )/30 | X    | 31    | 30   | ) /2 | 9)(2  | / 25  | i <mark>/</mark> 22 | 19    |

| ▶ 🔣 vreference[4:0]      | 11111   |      |        |       |        |                     |       |      |    |    |    |              |      |       |      |      |    |     |      |     |       |     |    | 1111 | 1   |     |    |      |      |      |      |      |    |      |      |    |       |       |      |      |       |      |      |       |       |                     |       |

| $\mathcal{V}_{0}$ clk_in | 1       |      |        |       |        |                     |       |      | 88 |    |    |              |      |       |      |      |    |     |      |     |       |     | 88 |      |     |     | 88 |      |      |      |      |      |    |      | 88   |    |       |       |      | 88   |       |      |      |       |       |                     |       |

| ▶ 🔣 data_out[4:0]        | 19      | U)   | 6 / 19 | ) /22 | 2)(25  | i <mark>(</mark> 27 | 29    | 30   | X  | 31 | 30 | 2            | )/2  | 7)(2  | 5)(2 | 22)  | 19 | 16  | (13) | 10  | (7)   | 5   | 3  | 2    |     | 1   | 2  | 3    | X    | X    | 7)(  | 10 🛛 | 13 | (16) | 19   | 22 | 25    | 27    | 29   | )(30 | Х     | 31   | 30   | ) /29 | 27    | 25                  | 22    |

| 🔓 clk_in_period          | 1000 ps |      |        |       |        |                     |       |      |    |    |    |              |      |       |      |      |    |     |      |     |       |     |    | 1000 | ps  |     |    |      |      |      |      |      |    |      |      |    |       |       |      |      |       |      |      |       |       |                     |       |

|                          |         |      |        |       | Fi     | ig.                 | 8 5   | SAI  | R/ | ٩D | C  | als          | zor  | ith   | ım   | in   | Х  | ili | nx   | Isi | im    | (si | im | ula  | tio | n t | im | ne ( | ) t  | 03   | 66   | ) n  | s) |      |      |    |       |       |      |      |       |      |      |       |       |                     |       |

| Messages                 |         |      |        |       |        |                     |       |      |    |    | Ĺ  |              | ,    |       |      |      |    |     |      |     |       | (   |    |      |     |     |    |      |      |      |      |      |    |      |      |    |       |       |      |      |       |      |      |       |       |                     |       |

| ₽- ♦ din_positive 16     | 16 (19  | 22 2 | 5 27   | 29    | 30     | 31                  |       | 30   | 29 | 27 | 25 | 22           | 19   | ) (1  | 6 (  | 13 ) | 10 | 7   | 5    | 3   | 2     | 1   |    | 2    | 3   | )5  | 7  | 1    | 0 (1 | 3    | 16   | 19   | 22 | 25   | 27   | 29 | ) (3( | ) (3) | 1    | 3    | 0 2   | 9 2  | 7 2  | 5 2   | 2 (19 | 9                   |       |

|                          | 1 11111 |      |        |       |        |                     |       |      |    |    |    |              |      |       |      |      |    |     |      |     |       |     |    |      |     |     |    |      |      |      |      |      |    |      |      |    |       |       |      |      |       |      |      |       |       |                     |       |

| 🔥 dk_in 🛛 0              |         |      |        |       |        | TWI                 |       |      | mu |    |    |              |      | ШП    |      |      |    |     |      | M   |       |     |    |      |     | IWI |    |      |      | UM   |      |      |    |      |      |    |       |       |      |      |       | UM   |      |       |       | TU                  |       |

| + data_out 19            | X (16   | 19 2 | 2 25   | 27    | 29     | 30                  | 31    |      | 30 | 29 | 27 | 2            | 22   | 2 )1( | 9 (1 | 6    | 13 | 10  | 7    | 5   | 3     | 2   | 1  |      | 2   | 3   | 5  | 7    | 1    | 0 )  | 3    | 16   | 19 | 22   | 25   | 27 | 29    | 30    | 3    |      | 3     | 0 29 | 9 2  | 7 2   | 5 22  | 2                   |       |

|                          |         |      |        |       |        |                     |       |      |    |    |    |              |      |       |      |      |    |     |      |     |       |     |    |      |     |     |    |      |      |      |      |      |    |      |      |    |       |       |      |      |       |      |      |       |       |                     |       |

Fig. 9 SAR ADC algorithm in modelsim (simulation time 0 to 360 ns)

Fig. 10 SAR ADC algorithm in modelsim (simulation time 0 to 720 ns)

Siavash Heydarzadeh

Afshin Kadivaryan