# Bias Stability of a-IGZO TFT and a new Shift-Register Design Suitable for a-IGZO TFT

Young Wook Lee, Sun-Jae Kim, Soo-Yeon Lee, Moon-Kyu Song, Woo-Geun Lee Min-Koo Han

**Abstract**—We have fabricated a-IGZO TFT and investigated the stability under positive DC and AC bias stress. The threshold voltage of a-IGZO TFT shifts positively under those biases, and that reduces on-current. For this reason, conventional shift-register circuit employing TFTs which stressed by positive bias will be unstable, may do not work properly. We have designed a new 6-transistor shift-register, which has less transistors than prior circuits. The TFTs of the proposed shift-register are not suffering from positive DC or AC stress, mainly kept unbiased. Despite the compact design, the stable output signal was verified through the SPICE simulation even under RC delay of clock signal.

*Keywords*—Indium Gallium Zinc Oxide (IGZO), Thin Film Transistor (TFT), shift-register

# I. INTRODUCTION

**A**MORPHOUS Indium-Gallium-Zinc-Oxide (a-IGZO) is a promising candidate for high performance TFT because it shows high field-effect mobility and on-current while has very low leakage current [1],[2] and also, can secure uniform TFT characteristics when fabricated in large area [3].

Some companies integrate shift-register, which generates gate-pulse signal, using amorphous silicon TFT (a-Si TFT) to reduce cost of driver ICs [4], [5]. Similar attempts were investigated by some researcher group to integrate shift-register using a-IGZO TFT instead of a-Si TFT [6], [7].

However, most shift-registers include transistor which gets clock signal (AC) or positive DC for gate input bias. Under that condition, the threshold voltage of TFT will be shifted positively, and the on-current will decrease [8]-[13], so that the TFT is not working properly as time passes.

In our research, we have fabricated a-IGZO TFT and investigated the stability under positive DC and AC bias stress. Likewise prior report, the threshold voltage shifted positively

Young Wook Lee is with the Electrical Engineering and Computer Science Department, Seoul National University, Seoul, Korea (phone: +82-880-7992; fax: +82-2-871-7992; e-mail: ywlee@emlab.snu.ac.kr).

Soo-Yeon Lee is with the Electrical Engineering and Computer Science Department, Seoul National University, Seoul, Korea (phone: +82-880-7992; fax: +82-2-871-7992; e-mail: xcloverx@emlab.snu.ac.kr).

Sun-Jae Kim is with the Electrical Engineering and Computer Science Department, Seoul National University, Seoul, Korea (phone: +82-880-7992; fax: +82-2-871-7992; e-mail: siglory@emlab.snu.ac.kr).

Moon-Kyu Song is with the Electrical Engineering and Computer Science Department, Seoul National University, Seoul, Korea (phone: +82-880-7992; fax: +82-2-871-7992; e-mail: mk86@emlab.snu.ac.kr).

Woo-Geun Lee is with Samsung Electronics, Yongin-Si, Korea (wg2.lee@samsung.com).

Min-Koo Han is with the Electrical Engineering and Computer Science Department, Seoul National University, Seoul, Korea (phone: +82-880-7992; fax: +82-2-871-7992; e-mail: mkh@snu.ac.kr). under those biases, and that caused reduction of on-current. In such a case, conventional shift-register circuit employing TFTs which stressed by positive bias will be unstable, may do not work properly. Therefore, we aimed to design shift-register circuit which is not suffering from positive DC or AC stress. This paper will show successful circuit design and simulation results that meet our goal.

## II.A-IGZO TFT FABRICATION AND CHARATERISTICS

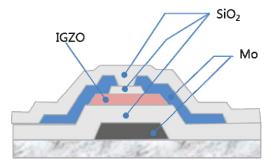

We fabricated the inverted-staggered etch stopper structure oxide-based TFTs. Gate metal (Mo) was deposited by DC sputtering on a glass substrate. SiO2 layer was deposited by plasma enhanced chemical vapor deposition (PECVD) for gate insulator and then active layer was deposited by sputtering. After active island patterning, etch-stopper layer was deposited and patterned to prevent back surface damage from post process. Source/drain electrodes (Mo) were deposited by sputtering and patterned. Finally, SiO2 layer was deposited for passivation. After fabrication finished, TFT was annealed at 300 °C in air condition. Figure 2 shows the schematic cross-section view of fabricated a-IGZO TFT.

Fig. 1 Schematic image of fabricated a-IGZO TFT

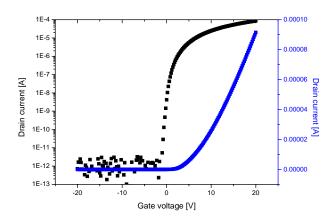

We measured the TFT of which width/length ratio is 50um/10um. To analyze transfer characteristics with semiconductor analyzer (Agilent B1500A), the gate voltage was swept from -20 V to 20 V at 0.2V step and drain voltage was 10 V while source electrode was grounded.

The measured transfer curve is showed in Figure 2. The saturation mobility is  $8.62 \text{ cm}^2/\text{Vs}$  and the threshold voltage is 0.67V. The steep sub-threshold slope (0.34V/decade) suggests that a-IGZO TFT has lower sub-gap state near conduction band edge (Ec) than a-Si TFT.

## World Academy of Science, Engineering and Technology International Journal of Electrical and Computer Engineering Vol:5, No:4, 2011

Fig. 2 Transfer curve of a-IGZO TFTs

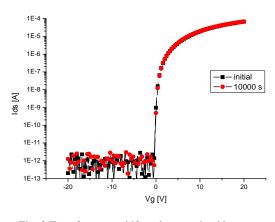

To investigate bias stability of fabricated a-IGZO TFT, negative and positive bias was applied to the TFT, respectively. Negative bias condition is that gate to source voltage (Vgs) is -20V and drain to source voltage (Vds) is kept at 10V. The initial and final (after 10000 seconds) transfer characteristics are exhibited in figure 3. We can hardly see the differences in both curves. That is, a-IGZO TFT is stable under negative bias stress.

Fig. 3 Transfer curve shift under negative bias stress : Vgs=-20V, Vds=10V

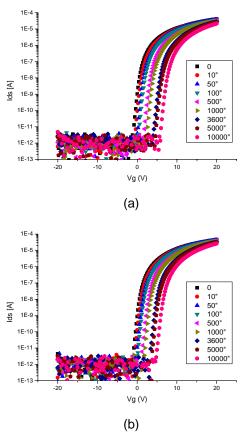

To investigate the stability under positive bias stress, we tested electrical bias both DC and AC stress. Figure 2 (a) shows the transfer curve shift under positive DC stress at Vgs=Vgd=30V for 10000 seconds. Threshold voltage shift (Vth shift) is about 6V, a large value considering relatively short time. Figure 2 (b) shows the transfer curve shift under AC stress, which has 50% duty ratio, 20us pulse width and  $V_{high}$ =30V,  $V_{low}$ =0V. Vth shift under AC stress is about 5V, this value is a bit lower than that of DC stress but still large value. TFTs under these conditions will not work well in short period. These trends of Vth shift are agreement with previous reports [8]-[13]. Therefore, it is desirable to design circuit with TFTs which avoid suffering from positive DC or AC (=clock) for gate input bias.

Fig. 4 Transfer curve shift under bias stress : (a) positive DC (Vgs=Vgd=30V), (b) positive AC (duty=50%, pulse with=20us, V<sub>high</sub>=30V, V<sub>low</sub>=0V, Vd=Vs=0V)

#### III. SHIFT-REGISTER DESIGN

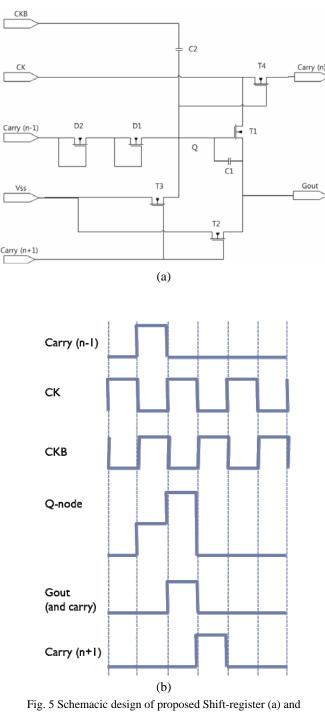

We devised novel compact design of shift-register. Figure 3 (a) represents schematic design of our proposed shift-register and Figure 3 (b) exhibits schematic input/output signal. Carry signal from previous stage [carry (n-1)] enters Q-node through D2 and D1 diodes, and then Q-node is floated. CK signal varies from low state (Vss) to high state (Vdd). That makes current flow through T1, so that the potential of Gout and carry (n) will increase up to Vdd, also Q-node is boosted up to higher voltage by C1. When carry signal from next stage [carry (n+1)] enters into T2 gate and T3 gate, Gout and Q-node is reset to Vss, and then floated. We can verify there is none of transistors stressed by positive DC or AC (=clock).

As mentioned above, after turning-off of T3, Q-node is floated and coupled to CK due to parasitic capacitance between CK and T1. That makes Q-node potential unstable, in other words, a ripple voltage is generated by coupling to CK.

input/output signal (b)

The role of C2 is to stabilize or alter phase of Q-node ripple. C2 supplies opposite charges to Q-node by coupling to CKB. We can estimate theoretically the ripple voltage of Q-node as below,

$$\Delta V = \frac{C_{\text{parastic}} - C_2}{C_{\text{parastic}} + C_2 + C_1} \times (V dd - V ss)$$

Where, C<sub>parastic</sub> indicates the capacitance between CK and T1 and makes Q-node unstable.

By above equation, we expect that if C2 is larger than  $C_{\text{parastic}}$ , we can convert the phase of Q-node ripple. Important meaning of converted phase of ripple is that when CK is high state, the ripple is low state, so that Vss potential of Gout is less affected by CK during hold time.

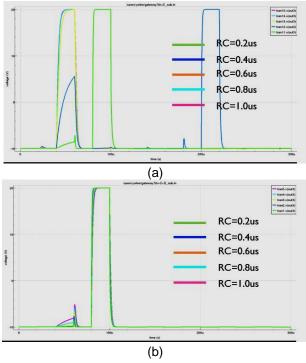

We simulated Gout by constructing cascade of shift-register, and show the results in Figure 4. We have verified that the larger clock delay is inputted, the worse Gout is produced. Therefore, it is desirable to consider RC delay of CK to verify reliability of circuit.

Figure 4 (a) shows the case of removing D2 diode from shift-register in Figure 3 (a). There are abnormal outputs except for 0.2us-RC. However, by employing D2, we can verify stable output in Figure 4 (b). Because D2 eliminates or lowers the carry noise, more stable carry signal can be inputted to D1.

Fig. 6 Simulation results of Gout :

(a) simulation w/o D2, (b) simulation w/ D2 diode (where, RC is time delay constant of clock signal)

# IV. CONCLUSION

We have fabricated a-IGZO TFT and investigated the stability under negative and positive bias, respectively. While a-IGZO TFT is stable under negative bias stress, it is severely shifted under positive DC/AC bias. Positive shift reduces the on-current, so that conventional shift-register circuit employing TFTs which stressed by positive bias will be unstable, may do not work properly. Therefore, we aimed to design shift-register circuit in which is no positive DC or AC stress. And we proposed a new 6-transistor shift-register, which has less transistors than prior circuits. The TFTs of the proposed shift-register are not suffering from positive DC or AC stress, mainly kept unbiased. Despite the compact design, the stable

output signal was verified through the SPICE simulation even under RC delay of clock signal.

# ACKNOWLEDGMENT

This research was supported by a grant(No. F0004062-2010-33)from Information Display R&D Center one of the Knowledge Economy Frontier R&D Program funded by the Ministry of Knowledge Economy of Korean government.

## References

- H. Yubata *et al.*, "High-mobility thin-film transistor with amorphous InGaZnO4 channel fabricated by room temperature rf-magnetron sputtering", Appl. Phys. Lett. 89, 112123 (2006).

- [2] H. Hosono *et al.*,"Recent progress in transparent oxide semiconductors: Materials and device application", Thin Solid Films 515 (2007).

- [3] J-H. Lee et al, "World's largest (15-inch) XGA AMLCD panel using IGZO oxide TFT, SID 08 Digest, PP.625 (2008)

- [4] S.H. Moon et al, US20070177438

- [5] Yong Ho Jang, US20060146978

- [6] Abbas Jamshidi-Roudbari, Shahrukh Akbar Khan and Miltiadis K. Hatalis, "High-Frequency Half-Bit Shift Register With Amorphous-Oxide TFT", IEEE ELECTRON DEVICE LETTERS, VOL. 31, NO. 4, (2010)

- [7] T. Osada, K. Akimoto, T. Sato, M. Ikeda, M. Tsubuku, J. Sakata, J. Koyama, T. Serikawa, and S. Yamazaki, "Development of driverintegrated panel using amorphous In-Ga-Zn-Oxide TFT," in Proc. SID Symp. Dig., vol. 40, pp. 184–187 (2009)

- [8] Jae Kyeong Jeong, Hui Won Yang, Jong Han Jeong, Yeon-Gon Mo, and Hye Dong Kim, "Origin of threshold voltage instability in indium-gallium-zinc oxide thin film transistors", Appl. Phys. Lett. 93, 123508 (2008)

- [9] Ken Hoshino, David Hong, Hai Q. Chiang, and John F. Wager, "Constant-Voltage-Bias Stress Testing of a-IGZO Thin-Film Transistors", IEEE TRANSACTIONS ON ELECTRON DEVICES, VOL. 56, NO. 7 (2009)

- [10] A. Suresh and J. F. Muth, "Bias stress stability of indium gallium zinc oxide channel based transparent thin film transistors", Appl. Phys. Lett. 92, 033502 (2008)

- [11] In-Tak Cho, Jeong-Min Lee, Jong-Ho Lee and Hyuck-In Kwon, "Charge trapping and detrapping characteristics in amorphous InGaZnO TFTs under static and dynamic stresses", Semicond. Sci. Technol. 24 (2009)

- [12] Sangwon Lee et al., "Electrical stress-induced instability of amorphous indium-gallium-zinc oxide thin-film transistors under bipolar ac stress", APPLIED PHYSICS LETTERS 95, 132101 (2009)

- [13] Tze-Ching Fung, Katsumi Abe, Hideya Kumomi and Jerzy Kanicki, "DC/AC Electrical Instability of R.F. Sputter Amorphous In-Ga-Zn-O TFTs", SID 09 DIGEST (2009)