# A Novel Low Power, High Speed 14 Transistor CMOS Full Adder Cell with 50% Improvement in Threshold Loss Problem

T. Vigneswaran, B. Mukundhan, and P. Subbarami Reddy

Abstract—Full adders are important components in applications such as digital signal processors (DSP) architectures and microprocessors. In addition to its main task, which is adding two numbers, it participates in many other useful operations such as subtraction, multiplication, division,, address calculation,..etc. In most of these systems the adder lies in the critical path that determines the overall speed of the system. So enhancing the performance of the 1-bit full adder cell (the building block of the adder) is a significant goal.Demands for the low power VLSI have been pushing the development of aggressive design methodologies to reduce the power consumption drastically. To meet the growing demand, we propose a new low power adder cell by sacrificing the MOS Transistor count that reduces the serious threshold loss problem, considerably increases the speed and decreases the power when compared to the static energy recovery full (SERF) adder. So a new improved 14T CMOS 1-bit full adder cell is presented in this paper. Results show 50% improvement in threshold loss problem, 45% improvement in speed and considerable power consumption over the SERF adder and other different types of adders with comparable performance.

*Keywords*—Arithmetic circuit, full adder, multiplier, low power, very Large-scale integration (VLSI).

#### I. INTRODUCTION

THE adder is one of the most critical components of a processor, as it is used in the arithmetic logic unit (ALU), in the floating-point unit, and for address generation in case of cache or memory access [3]. Increasing demand for mobile electronic devices such as cellular phones, PDA's, and laptop computers requires the use of power efficient VLSI circuits. There are two basic approaches to reduce power consumption of circuits in scaled technologies: reducing the dynamic power consumption during the active mode operation of the device and the reduction of leakage current during the stand-by mode [5]. The power consumption of a CMOS digital circuit can be represented as

$$P = f C V_{dd}^{2} + f I_{short} V_{dd} + I_{leak} V_{dd}$$

(1)

Where *f* is the clock frequency, *C* is the average switched Capacitance per clock cycle,  $V_{dd}$  is the supply voltage,  $I_{short}$  is the short circuit current, and  $I_{leak}$  is the off current [5]. In a well-optimized low power VLSI circuit, the 1<sup>st</sup> term of Equation (1) is by far the dominant.

Authors are SRMIST, Chennai, India ( e-mail: vigneshvlsi@gmail.com, mukundhan@engineer.com, psreddy40@hotmail.com ).

The stand-by power consumption is accounted for by the 3rd term. Using a lower  $V_{dd}$  is an effective way to reduce the dynamic power consumption since the 1st term is proportional to the square of  $V_{dd}$ . It should also be noted that The short circuit and leakage power dissipation are also strongly dependent on  $V_{dd}$ .

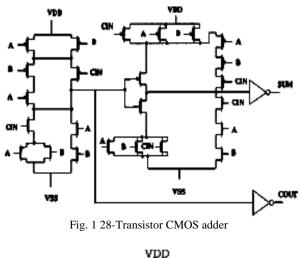

The lower the supply voltage is, the smaller the power consumption. However, using a lower  $V_{dd}$  degrades performance. The conventional adder uses 28 Transistors implemented in CMOS technique shown in Fig. 1.

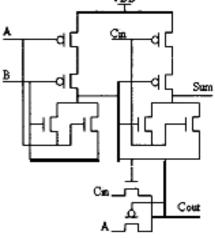

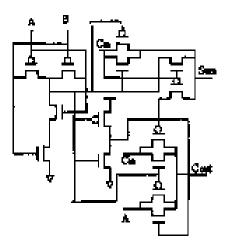

Fig. 2 Static energy recovery full (SERF) adder

A new full adder called Static Energy-Recovery Full adder (SERF) uses only 10 Transistors shown in Fig 2, which has the least number of transistors and is reported to be the best in power consumption, according to [3].

Many low-power adders using various pass transistors, such as the SERF [3] Compared to The complementary static CMOS adders, such low-power adders have the problem of threshold loss, i.e., the logic value 1 is not the value of  $V_{dd}$ and the logic value 0 may not be the value of 0. This kind of threshold-loss logic gates may not be used as widely as the complementary static CMOS gates. However, they are certainly useful in building up larger circuits such as multiplebit input adders and multipliers. In this paper, we propose a new approach to designing many 14-transistor full adders. Our aim is to reduce the threshold-loss problem which exists in previous designs [3]; however, our new adder cells are useful for designing larger circuits such as multipliers despite increase in transistor count by four per cell.

The rest of the paper is organized as follows: In Section II we briefly describe the previous work existing in the literature. In Section III we propose the new improved 14T adder. In Section IV we present the simulation results. In Section V, we draw the conclusions.

#### II. PREVIOUS WORK

The full adder operation can be stated as follows: Given the three 1-bit inputs A, B, and Cin, it is desired to calculate the two 1-bit outputs Sum and Carry, where

Sum = (A xor B) xor CinCarry = A and B + Cin (A xor B)

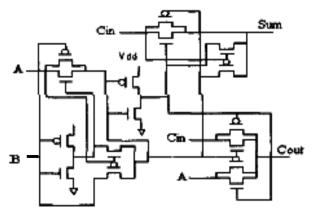

Several designs of low power adder cells can be found in the literature [3] [4] [5]. The transmission function full adder [1], which uses 16 transistors, for the realization of the circuit, is shown in Fig. 3. For this circuit there are two possible short circuits paths to ground. This design uses pull-up and pulldown logic as well as complementary pass Logic to drive the load. The dual value logic (DVL) full adder [2] illustrated in Fig. 4 uses 23 transistors for the realization of the adder function. The DVL was developed to improve the characteristics of double pass transistor logic, which was designed to have the logic level high signal passed to the load through a P-transistor and the logic level low Drained from the load through an N-transistor. The Fourteen transistors fulladder [8], as the name implies, uses 14 Transistors to realize the adder function (See Fig. 5). The 14T full adder cell, like the transmission function full adder cell, implements the complementary pass logic to drive the load. The SERF design requires only 10 transistors to realize the adder function. Even though it has threshold loss problem, it is suited for low power design so far.

Fig. 3 The transmission function adder (TFA)

Fig. 4 The dual value logic (DVL) adder

Fig. 5 The fourteen Transistor (14T) adder

#### III. NEW ADDER DESIGN

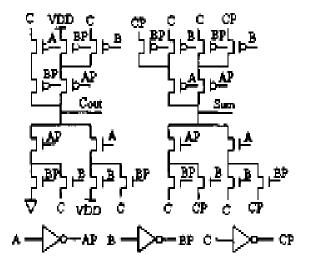

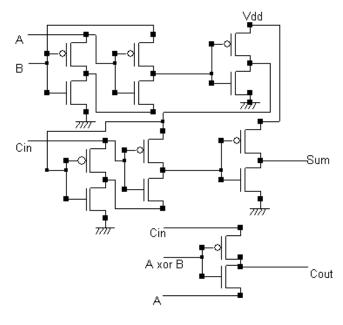

Our new improved 14T adder cell requires only 14 transistors to realize the adder function shown in Fig. 6. It produces the better result in threshold loss, speed and power by sacrificing four extra transistors per adder cell. Even though the transistor count increases by four per adder cell, it reduces the threshold loss problem, which exists in the SERF by inserting the inverter between XOR Gate outputs to form XNOR gate.

Fig. 6 New improved 14T Adder

Our newly proposed adders implement the Sum using XNOR-XNOR and Carry using PMOS - NMOS. We can also Build to produce Carry using NMOS-NMOS and PMOS-PMOS. But the delay and power dissipation of PMOS-NMOS is better than other two kinds of producing Carry. The proposed XNOR gate is designed by putting inverter at the output of the XOR gate in order to improve the threshold loss problem, which exists in the SERF adder. Out of the three methods, PMOS-NMOS based Carry gives the better result in power, speed and threshold loss problem.

### IV. EXPERIMENT DESCRIPTION AND RESULTS

We have performed experiments on newly designed 1-bit full adders along with the SERF adder and the conventional CMOS adder at the schematic level. The transistors have a channel length of 1.5 u and a channel width of 1.9 u using 1.2 Volt logic. Each circuit is simulated with the same testing conditions and the various results are shown in Graph1, Graph 2, Table I and Table II. The net lists of those adders are extracted and simulated using PSPICE on a Pentium IV machine.

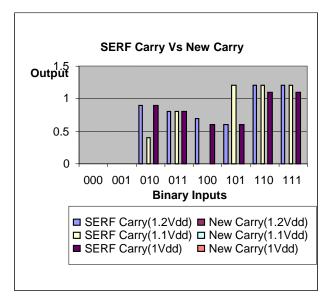

Graph 1 Sum comparison

Graph 1 and Graph 2 show the value of Sum and Carry for SERF and new improved 14 T Adder. The SERF does not provide logic 0 (approx 0.6 Volts) and logic 1(approx 0.9 Volts) for sum and Carry for all possible input combinations. But the new improved 14Tadder provides logic 0 (approx 0.3 Volts) and logic 1(1.2 volts) for sum and Carry for all possible input combinations. Thus the new improved 14T adder improves the threshold loss by 50% as compared to the SERF adder.

Graph 2 Carry comparison

Propagation delay is the time between the fastest input signal and the output signal. We use the first rising edge of all signals at the beginning of the second pattern cycle. The results are shown in Table I.

| TABLE I                   |                |                     |       |  |

|---------------------------|----------------|---------------------|-------|--|

| ADDER LATENCY (µ SECONDS) |                |                     |       |  |

| ADDER                     | SUM            | CARRY               | TOTAL |  |

|                           | DELAY[Sum(     | <b>DELAY[Carry(</b> | DELAY |  |

|                           | <b>0 to</b>    | 0 to                |       |  |

|                           | 1)+Sum(1to 0)] | 1)+Carry(1to 0)]    |       |  |

| SERF                      | 0.421          | 0.402               | 0.823 |  |

| NEW                       | 0.302          | 0.101               | 0.403 |  |

Tables I shows the accurate value of sum and carry delays from low to high and vice versa. From the Table I, we can conclude that the new improved 14T adder has less latency than the SERF adder. Hence its speed is 45% more than the SERF adder at  $1.2 V_{dd}$ .

Also the power dissipation of the SERF and new improved 14T adder at different Vdd<sub>.</sub> are tabulated in Table II.

| TABLE II<br>Power Dissipation (MW) |        |           |  |  |

|------------------------------------|--------|-----------|--|--|

| VDD                                | SERF   | NEW ADDER |  |  |

| 1.2V                               | 303.31 | 0.010     |  |  |

| 1.1V                               | 183.23 | 0.008     |  |  |

| 1.0V                               | 91.612 | 0.006     |  |  |

| 0.9                                | 30.531 | 0.005     |  |  |

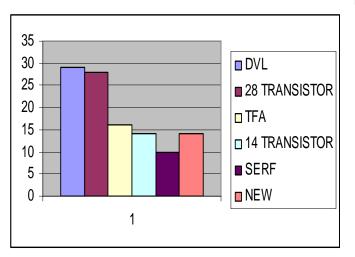

Graph 3 Transistor comparison

From the Table II, we can conclude that the SERF recovers 303mW at 1.2  $V_{dd}$  and the new improved 14T adder dissipates only 10 $\mu$ W. Hence we can build larger circuits with the help of our new adder cell which provides only small amount of power dissipation in the order of micro watts.

Graph 3 shows the SERF adder has less number of transistors per adder cell. Even though SERF occupies less area compared to new improved 14Tadder cell, the new improved 14T adder performance is very good in speed and power factors.

After the simulations, the new improved 14T full adders shown in Fig. 6 stand out as being the best along with the SERF adder and the other CMOS adders.

In power consumption at 1.2  $V_{dd}$ , new improved 14T adder consistently has better power consumption as shown in Table1.Our new improved 14T Adder cell reduces the threshold loss problem by 50% as compared to the SERF adder. Also its Speed is improved by 45% as compared to the SERF. Since our new adder cell dissipates small amount of power, we can call it as low power adder.

As mentioned earlier, the performance of many larger circuits are strongly dependent on the performance of the full adder circuits that have been used. The new improved 14transistor adder circuits presented in this study are good candidates to build these large systems, such as high performance multipliers with low power consumption. The small increase in Transistor count of these adders can significantly reduce the Latency of the systems built upon them.

## V. CONCLUSION

As mentioned earlier, the performance of many larger circuits are strongly dependent on the performance of the full adder circuits that have been used. The new improved 14T adder circuits presented in this study are good candidates to build these large systems, such as high performance multipliers with low power consumption. In this paper, we have presented a new improved 14T adder cell to construct full adders using only 14 transistors. Based on our extensive simulations, we conclude that our new adders consume considerably less power in the order of micro watts and have 45% higher speed and reduces 50% threshold loss problem compared to the previous different types of Transistor adders. With the help of this adder cell, we can design an efficient and high performance multiplier unit. In future, this kind of low power and high speed adder cell will be used in designing the digital FIR filter and its applications in various fields.

#### REFERENCES

- Nan Zhuang and Haomin Wu, "A new design of the CMOS full adder" IEEE Journal of Solid State Circuits, Vol. 27, No.5, pp. 840-844, May 1992.

- [2] V. G. Oklobdzija, M Soderstrand and B.Duchene "Development and Synthesis Method for Pass-Transistor Logic Family for High-Speed and Low Power CMOS" Proceedings of the 1995 IEEE 38th Midwest Symposium on Circuits and Systems, Rio de Janeiro, 1995.

- [3] R. Shalem, E. John, and L. K. John, "A novel low power energy recovery full adder cell," in Proc. IEEE Great Lakes VLSI Symp., Feb. 1999, pp. 380–383.

- N. Weste and K. Eshraghian, "Principles of CMOSVLSI Design", A [4] System Perspective. Reading, MA: Addison-Wesley, 1993.

- R. Zimmermann and W. Fichtner, "Low-power logic styles: CMOS [5] versus pass-transistor logic," IEEE J. Solid-State Circuits, vol. 32, pp.1079-1090, July 1997.

- [6] T. Callaway and E. Swartzlander, Jr., "Low power arithmetic components," IEEE in Low Power Design Methodologies. Norwell, MA: Kluwer, 1996, pp. 161-201.

- A.Chandrakasan,"Low-power CMOS digital design," IEEE JSSC", [7] vol.27, pp.473-484, Apr.1992.

- Ahmed M. Shams and Magdy A. Bayoumi, "A New Full Adder Cell for [8] low-power Applications", Proceedings of the IEEE Great Lakes Symposium on VLSI, 1998, pp. 45-49.

- [9] JohnRabaey, "Digital integrated circuits", Second Edison, 2003.

[10] K. P. Parhi, "Fast Low-Energy VLSI Binary Addition", Proceedings of the International Conference on Computer Design, 1997, pp.676-684.

- Gerard M. Blair, "Designing low power CMOS", IEEE Electronics & [11] Communication Engineering Journal, vol. 6, pp. 229-236, October 1994.

T.Vigneswaran has completed his BE in Electrical and Electronics engineering from Bharathidasan University in 2000 and M.E (VLSI DESIGN) from College of Engineering Guindy, Anna University in 2003. Currently he is working as a Lecturer in the SRM Institute of Science and Technology, Chennai.

B.Mukundhan has completed his BE in Information Technology from Madurai Kamaraj University in 2004 and is doing M.Tech (Embedded System Technology) in the SRM Institute of Science and Technology, Chennai.

P. Subbarami Reddy received B.E(Hons) in Electrical engineering from Andra University, in 1964, the M.Sc(Engg) from College of Engineering, Chennai in 1966 and PhD in Electrical Engineering from the IIT, Madras in 1972. Currently he is working as a professor in the SRM Institute of Science and Technology, Chennai..