# A Capacitive Sensor Interface Circuit Based on Phase Differential Method

H. A. Majid, N. Razali, M. S. Sulaiman, and A. K. A'ain

Abstract—A new interface circuit for capacitive sensor is presented. This paper presents the design and simulation of soil moisture capacitive sensor interface circuit based on phase differential technique. The circuit has been designed and fabricated using MIMOS' 0.35μm CMOS technology. Simulation and test results show linear characteristic from 36 – 52 degree phase difference, representing 0 – 100% in soil moisture level. Test result shows the circuit has sensitivity of 0.79mV/0.1<sup>0</sup> phase difference, translating into resolution of 10% soil moisture level.

Keywords—Capacitive sensor, interface, phase differential.

## I. INTRODUCTION

N the last decade, CMOS-MEMS micro sensor systems Ledevelopment has grown rapidly. The systems can measure many physical variables like position, accelerometer, angular speed and liquid level to detect the environmental changes [1]. Capacitive CMOS-MEMS sensors are widely used due to its high detection and low temperature sensitivity. However, due to the manufacturing limitation, the sensing capacitances are very small. Typically, these capacitances are on the order of femto-farads, and the noise from large parasitic capacitance, which is much greater than the sensor capacitance, would limit the detection sensitivity. Furthermore, the variations of the post-CMOS process can cause the capacitance mismatch. The mismatch of sensing capacitance would result in significant AC distortion in the output signal of the conventional demodulator. Hence, designing a low noise CMOS-MEMS sensing circuit is an important issue.

There are various methods used to detect the capacitance change. These include switched-capacitor based readout technique [2], relaxation oscillator [3], analog-to-digital conversion, diode-quad circuit, voltage (or current) to frequency (or time) conversion [4] and phase detection method [5].

The most common technique used for capacitive sensor's interface circuit is the switched-capacitor technique. Switched-capacitor technique converts the capacitance change to equivalent voltage level directly. It provides high resolution

H. A. Majid, N. Razali and M. S. Sulaiman are with the Microelectronics Department, Malaysia Institute of Microelectronic Systems (MIMOS), Technology Park Malaysia, 57000 Kuala Lumpur, Malaysia. (phone: 603-89955000 ext: 5801; fax: 603-89914234; (e-mail: yadi@mimos.my, nabihah.rz@mimos.my, shahiman.sulaiman@mimos.my).

A. K. A'ain is with the Faculty of Electrical Engineering, Universiti Teknologi Malaysia, UTM Skudai, 81310 Johor, Malaysia. (e-mail: abu@fke.utm.my).

for capacitors in the presence of parasitic capacitances [6]. Main drawback for switched-capacitor technique is the process variation of the capacitors. Capacitor's process variation of  $\pm 10\%$  could affect the readout circuit's accuracy and sensitivity. They are also prone to charge injection and clock feed-through problems.

In this paper, phase detection circuitry is used to design an interface circuit for Fringing Electric Field (FEF) soil moisture sensor. Phase detection technique determines the phase shift of a sinusoidal wave passing through the FEF sensor. The phase detection instrumentation has the advantage that it can detect a change of phase resulting from either change of effective resistance or capacitance of the soil dielectric [5]. Phase detection circuit is immune to the surrounding noise since it detects only the phase shift. Process variation does not have big impact on circuit performance since it does not contain any capacitor. The phase detection circuit can be designed such that it can be easily integrated with processing unit such as microprocessor.

This paper is divided into four additional sections. Principles of FEF sensing and circuit requirements are explained in section II and circuit implementation is presented in section III. Section IV presents simulated results, test result and physical layout. Finally, the conclusions are drawn in section V.

## II. ARCHITECTURE

### A. FEF Moisture Sensor

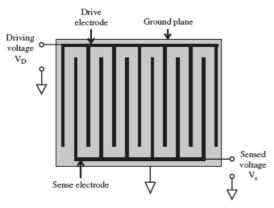

FEF moisture sensor uses fringing field capacitance (Fig.1) configuration, rather than the well-known parallel plate capacitance configuration. The fringing field capacitance is used to project the sensing electric field into the surrounding material [7]. Fig. 1 shows the schematic of an interdigitated fringing electric field sensor connected to a voltage sensing circuit. When an AC voltage signal is applied to the driving electrodes, the sensor generates a fringing electric field. The field strength and distribution pattern depend both on the input voltage signal and the sensor geometry.

### World Academy of Science, Engineering and Technology International Journal of Electronics and Communication Engineering Vol:3, No:7, 2009

Fig. 1 Schematic representation of a fringing electric field sensor connected in voltage sensing configuration with its back plane grounded.

FEF sensor can be modeled as an RC network as shown in Fig. 2. Admittance (Y), relates to capacitance and conductance through the following equation.

$$Y = \frac{1}{Z_S} = j\omega C_S + G_S \tag{1}$$

Expanding the equation, Capacitance change can be a function of output voltage, input voltage, frequency, interface circuit load and phase-shift through the following equation.

$$C_S = \left(\frac{V_O}{\omega R_L (V_O - V_i)}\right) * \sin(\theta)$$

(2)

The equation (2) can be further simplified by setting all variables except phase-shift to be constant. As a result, a linear characteristic between capacitance change  $(C_s)$  and phase shift are shown in the following equation.

$$C_{S} = K * \sin(\theta) \tag{3}$$

When an AC sinusoidal signal is passed through FEF sensor, the signal will suffer phase shift depending on the values of its equivalent RC network. Since the phase shift imparted on the signal depends upon the soil permittivity, detection of phase gives a measure of soil moisture concentration. Sensor measurement shows that phase difference for dry soil is 52 degree while for water is 36 degree. Hence, conclusion can be made that phase difference is inversely proportional to soil moisture content and range from 36 to 52 degree is the phase difference which the interface circuit must be able to detect. In order to get accuracy of ~1% for the soil moisture reading in volumetric water content (VWC), accuracy of phase detection circuit must be 0.1 degree or better. Table I shows the requirement for FEF sensor interface circuit.

TABLE I

REQUIREMENTS FOR FEF SENSOR INTERFACE CIRCUIT

| No. | Description           | Specification                     |

|-----|-----------------------|-----------------------------------|

| 1   | Phase detection range | 36 <sup>0</sup> - 52 <sup>0</sup> |

| 2   | Resolution            | $0.1^{0}$                         |

| 3   | Number of points      | 160 points                        |

#### III. CIRCUIT IMPLEMENTATION

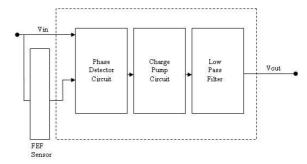

Diagram of the proposed interface circuit is depicted in Fig. 2. It consists of 3 main components; phase detector, charge pump and low pass filter. An AC signal is supplied to FEF sensor and the same signal is compared with output from FEF sensor to detect any phase difference. Charge pump and low pass filter converts pulse width from phase detector circuit to equivalent DC voltage.

Fig. 2 Block diagram of FEF sensor interface circuit.

# A. Phase Detector Circuit

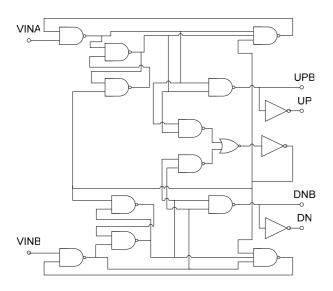

A phase detector circuit is a frequency mixer or analog multiplier circuit. The phase detector circuit compares the output signal from the FEF sensor with the reference signal (Vin). In this design, a conventional Phase Frequency Detector (PFD) circuit has been used. The Vin signal is connected to **VINA** port in the PFD circuit whereas output signal from the sensor is connected to **VINB** port, as shown in Fig. 3.

The PFD circuit has four output ports, UP, DN, UPB and DNB. UP signal is a pulse signal, where the width of the signal is equivalent to the delay or phase difference between the two input signals. DN signal is a very small pulse to reset the current in charge pump circuit. The UPB and DNB signals are the inverted signals of UP and DN. The four signals will be connected to switches in charge pump circuit to control the current flow in the charge pump circuit. The PFD circuit is also more immune to the process, supply voltage and temperature variations since it comprise of CMOS digital components.

Fig. 3 Schematic representation of Phase Frequency Detector

## B. Charge Pump Circuits

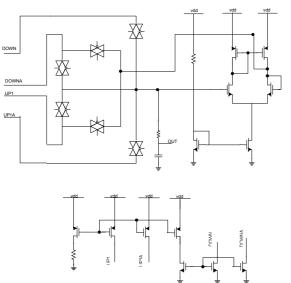

Charge pump circuit is a circuit consists of current source component and current sink component. The function of charge pump circuit is to control the current flow. It generates positive current levels in response to the frequency **Up** signal and negative current levels in response to the frequency **Down** signal. Each current source (UP1 and UP1A) and current sink (DOWN and DOWNA) draws and sinks 100μA of current. The net current provided by the charge pump is converted into DC voltage by the low pass filter.

Fig. 4 Schematic representation of a charge pump circuit. © MIMOS Berhad

# C. Low Pass Filter

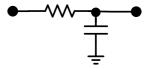

The main function of low pass filter in this circuit is to convert current generated by charge pump into equivalent DC voltage. This circuit uses 1<sup>st</sup> order low pass filter as shown in Fig. 5 to extract the DC level and further suppress the noise

level. The DC level of 1<sup>st</sup> order filter will carry phase difference which is related to soil moisture level.

Fig. 5 Low pass filter circuit

#### IV. SIMULATION RESULTS AND DISCUSSION

## A. Simulation Results

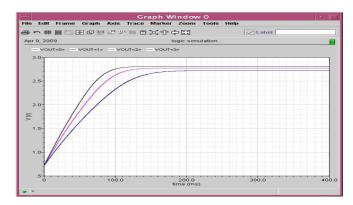

This circuit is simulated using MIMOS' 0.35um CMOS process technology. Table II summarizes the performance of the designed FEF readout circuit in three process corners simulation; typical, worst and best case. Simulation result shows the circuit's ability to detect phase change of 0.1° producing output voltage difference of 0.8 mV per 0.1° phase difference.

TABLE II SIMULATION RESULTS FOR 3 PROCESS CORNERS

|                  |           | Vout              |           |

|------------------|-----------|-------------------|-----------|

| Phase Difference | Worst     | Typical           | Best      |

|                  | 3.0 V     | 3.0 V             | 3.6 V     |

|                  | 90° C     | 27 <sup>0</sup> C | $0^0$ C   |

| $36^{0}$         | 2.72000 V | 2.44495 V         | 2.94643 V |

| 36.01            | 2.72100 V | 2.44503 V         | 2.94751 V |

| Sensitivity      | 0.0001 V  | 0.0008 V          | 0.00108 V |

Fig. 6 shows the worst case transient simulation for FEF readout circuit. Circuit's DC output range from 2.7 volt to 2.8 volt is simulated. The simulation shows that output signal is stable after 250ms.

Fig. 6 Transient simulation result. © MIMOS Berhad

# B. Test Results

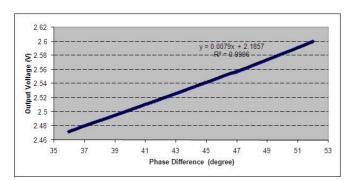

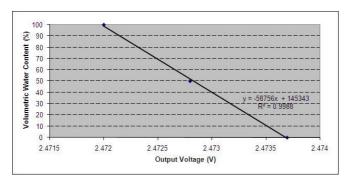

Test results shows that the circuit has good linearity from 36–52 degree phase difference as shown in Fig. 7. The change in phase is directly proportional to the output voltage with resolution of 0.79 mV/0.1°. Fig. 8 shows the relationship between VWC and output voltage where output voltage is inversely proportional to the VWC. Layout of the design can be seen in Fig. 9.

Fig. 7 Test result for output voltage vs. phase difference. © MIMOS Berhad

Fig. 8 Volumetric water content vs. output voltage. © MIMOS

Berhad

Fig. 9 Layout implementation of FEF interface circuit. © MIMOS Berhad

## V. CONCLUSION

A readout circuit for FEF capacitive sensor based on phase differential technique has been designed and simulated using MIMOS'  $0.35\mu m$  CMOS technology. In this design, type IV of phase frequency detector circuit is used together with charge pump and low pass filter to produce DC voltage proportional to phase difference. Simulation result shows a linear characteristic from 36-52 degree phase difference, representing 0-100% in soil moisture level. Sensitivity of  $0.79 mV/0.1^0$  phase difference has been achieved, translating into resolution of 10% soil moisture level.

#### REFERENCES

- T. C. Lu, Y. J. Huang and H. P. Chou, "A Novel Interface Circuit for Capacitive Sensors Using Correlated Double Sampling Demodulation Technique", in Proc. 2008 Second International Conference on Sensor Technologies and Applications, pp. 396-400.

- [2] A. Heidary and G. C. M. Meijer, "A Low-Noise Switched-Capacitor Front End for Capacitive Sensor", *IEEE SENSORS*, 2007, pp. 40-43.

- [3] R.B. McIntosh and M. E. Casada, "Fringing Field Capacitance Sensor for Measuring the Moisture Content of Agricultural Commodities," *IEEE Sensors Journal*, Volume 8, No. 3, 2008, pp:240-247.

- [4] A. Srivastava, M. R. Gumma, J. Cherukuri, "Readout interface circuits for MOS C-V sensors," Proc. of 37<sup>th</sup> Midwest Symposium on Circuit and Systems, 1994, pp:187-190.

- [5] J. Das, S. Dey, S. M. Hossain, Z. M. C. Rittersma and H. Saha, "A Hygrometer Comprising a Porous Silicon Humidity Sensor with Phase-Detection Electronics," *IEEE Sensors Journal*, Volume 3, Issue 4, 2003, pp. 414-420.

- [6] P. D. Dimitropoulos et al, "A Low-Power/Low-Noise Readout Circuit for Integrated Capacitive Sensors," *IEEE Sensors Journal*, Volume 6, No. 3, 2006, pp. 755-769.

- [7] G. de Rosny et al. "Numerical Modeling of a Capacitance Probe Response," Soil Science Society of America Journal, vol. 65, 2001, pp. 13-18.

- [8] J.F. Posada, J. J. Liou and R.N. Miller, "An Automated Data Acquisition System for Modeling the Characteristics of a Soil Moisture Sensor," *IEEE Transaction on Instrumentation and Measurement*, 1991, Volume 40, No. 5, pp. 836-841.

- [9] Behzad Razavi, "Design of analog CMOS integrated circuits," McGraw-Hill, 2001.

- [10] MIMOS Invention.