# Preparation of Porous Metal Membrane by Thermal Annealing for Thin Film Encapsulation

Jaibir Sharma, Lee JaeWung, Merugu Srinivas, Navab Singh

Abstract—This paper presents thermal annealing de-wetting technique for the preparation of porous metal membrane for Thin Film Encapsulation (TFE) application. Thermal annealing de-wetting experimental results reveal that pore size formation in porous metal membrane depend upon i.e. 1. The substrate at which metal is deposited, 2. Melting point of metal used for porous metal cap layer membrane formation, 3. Thickness of metal used for cap layer, 4. Temperature used for formation of porous metal membrane. In order to demonstrate this technique, Silver (Ag) was used as a metal for preparation of porous metal membrane on amorphous silicon (a-Si) and silicon oxide. The annealing of the silver thin film of various thicknesses was performed at different temperature. Pores in porous silver film were analyzed using Scanning Electron Microscope (SEM). In order to check the usefulness of porous metal film for TFE application, the porous silver film prepared on amorphous silicon (a-Si) and silicon oxide was released using XeF<sub>2</sub> and VHF, respectively Finally, guide line and structures are suggested to use this porous membrane for robust TFE application.

**Keywords**—De-wetting, thermal annealing, metal, melting point, porous.

## I. INTRODUCTION

MICROELECTROMECHANICAL SYSTEM (MEMS) devices have achieved a great attention in industry and research groups in recent past due to their cutting edge applications, including sensors, optics and RF devices [1], [2]. MEMS packaging with controlled ambient is in much demand in order to provide the proper operating condition and protect the MEMS devices from the harsh environment [3], [4]. The bonding is a known commercialized technique and many products are available in the market. However, bonding is expensive technique in terms of occupying wide area per dice due to wide seal rings, wide dicing area requirement for dicing the stack of wafers. This results in a less number of devices per wafer [5], [6].

Thin film encapsulation (TFE) is emerging as an alternative technique in recent past due to the possibility of overall thickness reduction and area saving in seal ring as well as low cost from elimination of a cap wafer. This technique uses surface micromachining process such as deposition, etching and release steps to realize the encapsulation of MEMS devices. However, TFE technique suffers with issues like long release time and mass loading on MEMS devices during the sealing process. To solve these issues, many different approaches have been tried by researchers and reported in the

Jaibir Sharma, Lee JaeWung, Merugu Srinivas, Navab Singh are with the MEMS Program, Institute of Microelectronics, Singapore (phone: +65-67705472; e-mail: sharmaj@ ime.a-star.edu.sg).

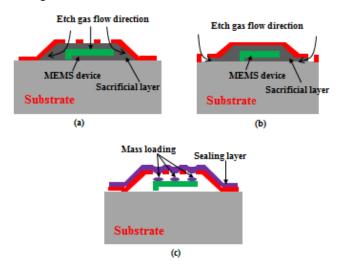

literature. These approaches are based on the location of etch channels or formation of pores (channel) in the cap layer to remove the sacrificial layer in TFE [7]-[11]. In one of the approach, the etch channels were distributed all over the cap layer as shown in Fig. 1 (a). The uniform distributions of many etch holes in the cap layer results in a short release time of TFE. However, it has a drawback of mass loading [7], [10] as sealing material may deposit on the MEMS device through etch holes as shown Fig. 1 (c). This mass loading may cause damage to the MEMS device or change the design parameter of the same. The mass loading is very critical for many devices like FBAR, SAW etc. as mass loading can change the operating frequency of these devices. In second approach, etch channels are fabricated at the sidewall of the cap layer (sidewall located channel scheme) as shown in Fig. 1 (b). The sidewall located channel scheme helps in preventing the mass loading on the MEMS device during sealing process. However, this scheme has a drawback of longer release time because sacrificial layer material should be removed through long etching path from sidewall to center of TFE as shown in Fig. 1 (b) [9]-[11]. On the other hand, porous cap layer with micro-or nano-etch holes may also be used to solve the above issues [12], [13]. In these approaches, the nano- or micron-sized pores play the role of etch channel which helps in fast removal of sacrificial layer and safe sealing of the TFE without mass loading on MEMS devices.

Fig. 1 Schematic diagrams of TFE for (a) uniformly distributed etch hole on the cap layer, (b) sidewall located etch channels and (c) mass loading on MEMS device during sealing for TFE realized using a approach as shown in (a)

There are many approaches in the literature for the

fabrication of nano- or micro-pores in thin film which has been used for TFE application. Lee et al. [14] used anodization technique to create pores in Chromium (Cr) thin film for releasing the structure under the porous membrane. However, these approaches are very costly and complicated by nature for the fabrication of pores. In this paper, a simple and cost effective technique has been discussed to fabricate the porous metal membrane. This technique simply used thermal annealing of thin metal film at particular temperature called dewetting temperature of metal to create the porous metal films. The pore size in the metal film can be controlled by controlling temperature of the annealing. However, pore size also depends on type's substrate and, metal etc. factors.

### II. POROUS MEMBRANE FORMATION

In this paper, we proposed a simple thermal annealing dewetting technique for formation of porous metal film (membrane). The pore size in the metal film can be controlled by i.e. 1. Proper selection of sacrificial layer (substrate) on which metal is deposited, 2. Proper selection of metal (cap layer) used for porous formation (lower melting point is preferred). However, cap layer metal selection should also be done by considering its selectivity with respect sacrificial etchant, 3. Thickness of metal used for formation of porous cap layer, 4. Temperature used for formation of porous in metal cap layer. The number of temperature cycles used for annealing, also affect the size of pore formation.

In this paper, silver (Ag) was used as a cap layer material and amorphous silicon (a-Si) was used as a sacrificial material. Three different annealing temperatures (250°C, 300°C and 350°C) and four different thicknesses (20nm, 50 nm, 100 nm and 200 nm) were used for the fabrication of porous membrane. Table I summarizes thickness of film and temperature ranges used for formation of porous Ag film on a-Si.

### III. RESULTS AND DISCUSSION

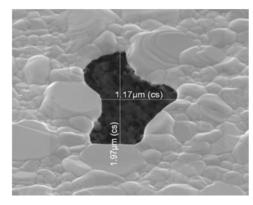

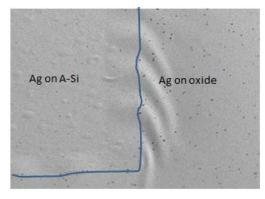

Fig. 2 shows the Scan Electron Microscope (SEM) image of pores in the membrane fabricated using 200 nm thick silver and annealed 350°C for 1 hour in nitrogen ambient. The pores size is more than 1 um in width and close 2 um in length was achieved. Grain formation of silver can be seen Fig. 2. Fig. 3 shows the SEM image of pores fabricated on a-Si and oxide substrate on same sample using 200 nm thick silver and annealed 350°C for 1 hour in nitrogen ambient. A-Si substrate was created on same sample by etching a window in oxide layer and filling the same with a-Si. Finally, CMP was performed for planarization. In Fig. 3, right side shows Ag on oxide and left side Ag on a-Si window. It can be observed from image that there are large number and big size of pores formation on oxide substrate. However, less number and small size pores are formed on a-Si substrate. This means that oxide surfaces are more favorable for fabrication silver porous membrane.

Table I shows different thickness and their behavior at three different temperatures. It can be observed that de-wetting become serious for very thin silver (Ag) film. A 20 nm thin Ag film shows good pores formation at 250°C. However, same thickness gets severely de-wet at 300°C. The severity of de-wetting of metal film depends on annealing temperature. Thicker film may severely de-wet at higher temperature. For example, 50 nm Ag film form a good pores at 250°C and 300°C. However, it gets severely de-wet at 350°C as can be seen Table I. At the same time, very thick metal may not dewet at all as can be seen from table that 200 nm silver films does get de-wet at 250°C and 300°C, respectively and pore formation only starts at 350°C. It means that formation of pores and their size depend on cap layer metal thickness, annealing temperature used for de-wetting. To de-wet thicker film, longer time and higher temperature is required.

Fig. 2 SEM image of the pores fabricated by annealing 200 nm silver film at  $350^{\circ}$ C for 1 hour

Fig. 3 SEM image of the pores fabricated on a-Si and oxide substrate

A. Porous Metal Membrane for Thin Film Encapsulation (TFE) Application

In order to check the feasibility of these porous metal membranes as a cap layer for TFE application, sacrificial a-Si and oxide were etched through small pores in the porous metal membrane.

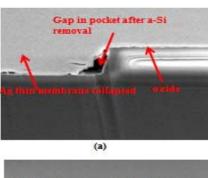

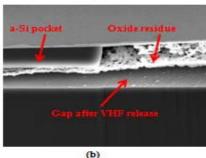

Fig. 4 (a) shows FIB–SEM cross-section image of the sample where a-Si sacrificial was etched with the help of Xenon Fluoride (XeF<sub>2</sub>). It can observed from the image that sacrificial a-Si was removed through pores and Ag thin membrane collapsed after a-Si sacrificial layer removal. Fig. 4 (b) shows the FIB–SEM cross-section image of the similar sample where oxide is considered as a sacrificial layer and

etched with the help of Vapour Hydrofluoric (VHF) through small pores. It can be observed from the image that oxide sacrificial was etched through pores. However, there was oxide residues left behind. These residues [15] are very common after VHF process for PECVD oxide which is usually deposited with recipe that includes NH<sub>3</sub> gas.

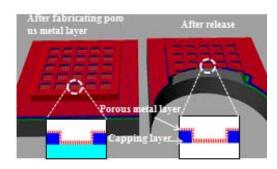

As observed in Fig. 4 (a) that thin porous Ag membrane is not strong enough to use as a structural cap layer for TFE application. On releasing the sacrificial layer, this porous Ag membrane collapses on to the substrate and hence not useful for TFE. In order to use this thin porous Ag film as a cap layer for TFE application, a second cap layer such as oxide or a-Si material (depending upon use of sacrificial material) can be prepared in the form of net on sacrificial layer and metal porous film can be formed above it as shown in Fig. 5. The

second cap layer have small patterned etch hole in it. Pores formed on these etch holes makes sacrificial layer accessible to sacrificial etchant. Sacrificial layer is etched through these pores available on etch holes. TFE can be released through these small pores. After releasing TFE, it is sealed by depositing sealing layer. This should be noted here that mass loading on encapsulated device is reduced as sealing material does not fall on device due to very small pore size. In order to reduce mass loading (require small pore size) and fast releasing (require beg pore size) which are opposite requirement by nature, there is need to optimize metal thickness and temperature value for annealing. From Table I, it is clear that one can select proper thickness and temperature for the fabrication of porous cap layer membrane to achieve fast releasing and less mass loading.

TABLE I SEM IMAGE FOR DIFFERENT THICKNESS OF POROUS SILVER FILM FABRICATED AT DIFFERENT TEMPERATURE

| Annealing   | Thickness of Ag film |       |                  |              |        |              |

|-------------|----------------------|-------|------------------|--------------|--------|--------------|

| Temperature | 20 nm                | 50 nm |                  | 100nm        |        | 200 nm       |

| 250°C       | ~100nm               |       | ~1µm             | No dewetting |        | No dewetting |

| 300°C       | No connection        |       | ~100nm           |              | ~1µm   | No dewetting |

| 350°C       | Serious dewetting    |       | No<br>connection |              | ~100nm | ~1µm         |

Fig. 4 FIB-SEM image of the samples after: (a) XeF<sub>2</sub> (b) VHF,

Fig. 5 Schematic diagrams of TFE by formation of strong net structure in second cap layer and porous metal on it

# IV. CONCLUSION

This paper demonstrates the porous metal layer formation by using a simple thermal annealing technique. The size of pores can be controlled by substrate, thickness of metal, temperature and selection of metal. This work also successfully demonstrates the removal of a-Si and oxide sacrificial layer through pores generated using thermal annealing technique. This paper also outline how this porous

### World Academy of Science, Engineering and Technology International Journal of Materials and Metallurgical Engineering Vol:9, No:9, 2015

metal can be used as a robust cap layer for encapsulating MEMS device without mass loading during sealing.

### REFERENCES

- [1] G. H. Mohamed, The MEMS Handbook, 2nd ed., New York, USA: Taylor & Francis, 2002.

- [2] M. Perlmutter and L. Robin High-Performance, "Low Cost Inertial MEMS: A Market in Motion!" Position Location and Navigation Symposium (PLANS), 2012, pp.225-229.

- [3] R. R. Tummala and E. J. Rymaszewski "Microelectronics Packaging Handbook", 2nd ed., Massachustts, USA: Kluwer Academic Publishers 1989.

- [4] K. Najafi, "Micropackaging Technologies for Integrated Microsystems: Applications to MEMS and MOEMS", Micromaching and Microfabrication Process Technology VII, Proc. Of SPIE Vol. 4979, 2003, pp.1-19.

- [5] Lutz M. Partridge, B. Kim, M. Hopcroft, R. N. Candler, T.W. Kenny, "MEMS Resonators: Getting the Packaging Right", in: SEMICON-Japan, 2005.

- [6] H. Stark and K. Najafi, "A Low-Temperature Thin-Film Electroplated Metal Vacuum Package", J. Microelectromech. Syst., vol. 13, 2004, pp. 147–157.

- [7] V. Lindroos, M. Tilli, A. Lehto and T. Motooka, Handbook of Silicon Based MEMS Materials and Technologies, 1st ed., Elsevier, chap 38, 2010, pp. 569-574.

- [8] J. L. Pornin, C. Gillot, G. Parat, F. Jacquet, E. Lagoutte, N. Sillon, G. Poupon, F. Dumont, "Wafer Level Thin Film Encapsulation for BAW RF MEMS.", Electronic Components and Technology Conference, 2007, pp. 605-609.

- [9] C. Gillot, J.L. Pornin, A. Amaud, E. Lagoutte, N.Sillon, J.C. Souriau, "Wafer Level Thin Film Encapsulation for MEMS", Electronic Components and Technology Conference, 2005, pp. 243-247.

- [10] US patent 7,344,907 B2 Mar. 18, 2008

- [11] C. O'Mahony, M. Hill, Z. Olszewski and A. Blake, "Wafer-Level Thin-Film Encapsulation for MEMS", Microelectronic Engineering vol. 86, 2009, pp. 1311–1313.

- [12] R.H. Rico, B. Du Bois, A. Witvrouw, C. Van Hoof, J.-P. Celis, "Fabrication of Porous Membranes for MEMS Packaging by One-Step Anodization in Sulfuric Acid", J. Electrochem. Soc. 154 (9) K74 – K78, 2007

- [13] J. Zekey, S. D Tezcan, J.-P. Celis, R. Puers, C. Van Hoof, and H.A.C. Tilmans, "Wafer-Level Thin Film Vacuum Packages for MEMS using Nanoporous Anodic Alumina Membrane", Transducers conference, 2011, pp. 975-977.

- [14] B. K. Lee, D. H. Choi and J. B. Yoon "Use of nanoporous columnar thin film in the wafer level packaging of MEMS devices" J. Micromech. Microeng. 20 045002 (9pp), 2010.

- [15] W. I. Jang, C. A. Choi, M. L. Lee, C. H. Jun and Y. T. Kim "Fabrication of MEMS devices by using anhydrous HF gas-phase etching with alcoholic vapor" J. Micromech. Microeng. 12, 297–306, 2002.